Процессор персонального компьютера. Назначение, функции, классификация процессора (Арифметико-логическое устройство)

Содержание:

ВВЕДЕНИЕ

В современном мире, где царят информационные технологии и где электронно-вычислительные устройства основательно закрепились в жизни человека, уже практически невозможно найти область человеческой деятельности, где не понадобилось бы электронно-вычислительное устройство.

Область использования данных электронных устройств безгранична и активно расширяется, что в свою очередь значительно влияет жизнь и деятельность человеческого общества.

С тех пор, как человечество осознало понятие количества, разрабатывались и применялись различные приспособления для отображения количественных эквивалентов и операций над величинами. Человечество стремилось автоматизировать свои вычислительные операции, что позволило человечеству пройти путь от механических вычислительных машин до создания более совершенны х - электронно-вычислительных машин (ЭВМ).

Актуальность данной курсовой работы обусловлена тем, что электронные устройства с главным вычислительным элементом в виде центрального процессора, прочно вошли в жизнь человеческого общества, но многие даже представления не имеют о сущности используемого электронного устройства и что в нём осуществляет полезные вычисления, для корректной работы для ожидаемого поведения данного устройства.

Объектом данной курсовой работы является центральный процессор.

Целью данной работы является изучение понятия центрального процессора, структурного состава центрального процессора, его архитектуру, функции и назначение.

Для достижения поставленных целей, были определены следующие задачи:

- Определить понятие «центральный процессор»;

- Изучить состав и архитектуру центрального процессора;

- Рассмотреть функции, а также назначение центрального процессора.

ГЛАВА 1. ЦЕНТРАЛЬНЫЙ ПРОЦЕССОР

Процессор или центральное процессорное устройство (ЦПУ, CPU, от англ. Central Processing Unit) является неотъемлемой частью компьютерной системы, которая выполняет все операции и функции программы. Он известен как процессор, по причине того, что каждая исполняемая инструкция должна пройти через него перед выполнением.

В общем случае, как установлено в ГОСТе: «процессор — это функциональная часть вычислительной машины или системы обработки информации, предназначенная для интерпретации программ». [1, c. 4] Непосредственно о центральном процессоре указано, что центральный процессор — это «процессор, выполняющий в данной вычислительной машине или системе обработки информации основные функции по обработке информации и управлению работой других частей вычислительной машины или системы». [1, c. 4]

Центральный процессор выполняет все базовые арифметические, логические, управляющие и операции ввода-вывода по инструкциям (командам, программному коду), которые координируют работу всех устройств компьютера, будучи закодированы и расположены в памяти. Инструкции могут быть от любых устройств ввода-вывода, таких как клавиатура или мышь, центральный процессор считывает, выполняет и отображает на экране монитора.

В ГОСТе сказано, что инструкция — это «однозначно определенное действие, выполняемое устройством вычислительной машины и составляющее выполнение команды или реакцию на определенные условия» [1, c.7], иначе говоря, простое и конечное действие, для выполнения которого центральному процессору нет необходимости получать дальнейшую детализацию. Объединение последовательности таких инструкций, которое ведёт к достижению определённой цели, именуется программой.

С появлением более совершенных технологий компьютеры стали выполнять целый набор инструкций.

«Набор инструкций – словарь, состоящий из команд, понятных данной архитектуре.» [3, c. 100]

Инструкции, в общем, состоят из двух частей — операционной и операндной. Операционная часть включается в себя данные о операциях, необходимые для выполнения центральным процессором. Операндная часть передаёт центральному процессору операнды - то, над чем предстоит работать именно центральному процессору, эта часть обрабатывает до двух операндов команды, в частности, это значения операндов, прямые либо косвенные ссылки на регистры центрального процессора, содержащие операнды, адрес ячейки памяти, регистры процессора и т. д.

Центральный процессор содержит в себе быструю память, сравнительно небольшого объёма, которая хранит в себе временные данные, в свою очередь эта память содержит регистры, которые выполняют конкретные задачи.

Также существует «регистровый файл — небольшое запоминающее устройство, которое состоит из совокупности регистров размеров в одно слово, каждый имеет своё уникальное имя. Устройство вычисляет новые значения данных и адресов.» [5, с. 22]

Все регистры равны по размеру. В каждом регистре содержится единственное число в определённом диапазоне, где верхний порог зависит от размера самого регистра.

Любой процессор имеет в своём составе самый важный регистр, хранящий логический адрес исполняемой инструкции и который указывает, какую команду центральному процессору необходимо выполнить следующей, называется он счётчик команд, хотя название не совсем корректно «поскольку он ничего не считает, но этот термин употребляется повсеместно»[2, с. 77], также используется термин — Instruction Pointer (указатель инструкции).

Выполнение последовательности инструкций осуществляется следующим образом: исполнив очередную инструкцию значение указателя инструкции инкрементируется, а если инструкция занимает больше памяти, то указатель увеличивается на длину инструкции.

Для обеспечения перехода в программе, выполняются специальные инструкции, модифицирующие, в процессе своего выполнения, содержимое счётчика указателя инструкции, а исполняемая на тот момент инструкция помещается в специальный элемент центрального процессора — регистр команд.

Инструкции делятся на линейные и инструкции передачи управления, первые, в зависимости от их позиции в памяти, исполняются по нарастанию адреса, а вторые, те что содержат в себе логический адрес следующей выполняемой инструкции, называемые — команды вызовов и переходов.

Инструкция может быть нарушена исключениями и прерываниями, невзирая на то, что порядок выполнения команд чётко предписывается кодом.

Исключения — это специальные условия, например ошибки, при выполнении которых инструкция передаёт управление обработчику.

В ГОСТе указано определение, что прерывание — это «операция процессора, состоящая в регистрации предшествующего прерыванию состояния процессора и установлении нового состояния. Прерывание является реакцией процессора на некоторые условия, возникшие в процессоре или вне его.»[1, c.7] Иначе говоря, это сигнал центральному процессору, например от контроллера устройств, о том, что есть необходимость оперативно прервать его текущую деятельность в пользу более приоритетных задач. Кроме того, последовательность инструкций может изменяться по сигналу перезапуска процессора.

Центральное процессорное устройство изначально, как термин, обозначало тип вычислительных машин, специализирующихся на решениях вычислительно-трудоёмких программ, но в связи с достаточно похожим, да и в принципе отвечающих довольно точно, по назначению и функциям имевшихся в те времена центральных процессоров компьютера, этот термин непринуждённо перекочевал на обозначение главных вычислительных элементов персональных компьютеров.

Данный термин и его аббревиатуру ЦПУ (CPU) стали применять, имея в виду компьютерные системы, в начале 1960-х годов. С того времени центральный процессор прошёл через множество изменений в архитектуре, реализации и в общем устройстве, но, несмотря на изменения, основные функции, которые выполняет данное устройство, остались прежние.

Середина 1980-х годов, время, когда центральные процессоры, реализуемые набором индивидуальных чипов, именуемые микропроцессорами, почти полностью вытеснили иные типы процессоров, из-за этого термин, закреплённый за иными устройствами, стал всё более используемым в адрес микропроцессоров и в конце концов закрепился за обращением обывателей. Но, не смотря на общую востребованность использования данного термина как синоним слова, обозначающего микропроцессор, технически, это не корректно, ибо центральные процессоры, что являются истинными владельцами данного термина, до сих пор используются в разного рода суперкомпьютерах, которые реализованы в виде больших комплексных объединённых систем.

Первые типы центральных процессоров, реализовались отдельными составными элементами для оригинальных и не повторимых компьютерных систем. Позже, для экономической и скоростной оптимизации производства, производители компьютерных системы перешли от дорогого метода создания центральных процессоров, который был реализован для компьютера предназначенного для одной или нескольких узконаправленных программ, к серийному методу производства целого ряда отдельных типов(класса) многозадачных центральных процессоров.

Склонность производителей комплектующих элементов компьютера к стандартизации появилась, когда в мире процветала и бурно развивалась эпоха полупроводников, мини-компьютеров и мейнфреймов, а создание интегральных схем сделало стандартизацию ещё популярнее.

С разработкой микросхем, комплексность структуры центрального процессора ещё более возросла, а их размеры, наоборот, уменьшились.

Уменьшение размеров процессора и стандартизация позволили производителям основательно внедрить процессоры в быт современного общества, путём внедрения их в цифровые устройства.

Современные центральные процессоры распространены не только на высокотехнологические компьютерные системы, но также они присутствуют в современных автомобилях, игрушках, стационарных и мобильных телефонах и в прочих электронных бытовых устройствах.

Обычно современные центральные процессоры реализованы в виде микроконтроллеров, где, не считая вычислительного элемента, на кристалле можно найти дополнительные элементы в виде интерфейсов, памяти, портов и пр.

Современные вычислительные возможности микроконтроллера сравнимы с процессорами персональных ЭВМ десятилетней давности, а чаще даже значительно превосходят их показатели.

Центральный процессор размещают в разъёме для конкретного процессора на материнской плате, также над ним располагают вентилятор и радиатор для защиты от перегрева.

Объем оперативного запоминающего устройства (ОЗУ), скорость шины и объем кэш-памяти прямо влияет на производительность центрального процессора: чем больше мы используем, тем быстрее он может работать. Он состоит из нескольких компонентов, и каждый компонент функционирует в соответствии со скоростью процессора, что помогает быстрее выполнять инструкции, а также ускоряет работу компьютера. Существует ряд компаний, разрабатывающих процессорные чипы для процессоров, такие как Intel, AMD и Athlon, с различными моделями для более быстрого выполнения инструкций.

ГЛАВА 2. СОСТАВ ЦЕНТРАЛЬНОГО ПРОЦЕССОРА

Центральный процессор компьютера, как правило, состоит из следующих элементов:

- арифметико-логическое устройство;

- шины адресов и данных;

- регистры процессора;

- счетчики команд;

- кэш-память;

- математический сопроцессор чисел с плавающей точкой.

Рассмотрим состав центрального процессора подробнее.

2.1 Арифметико-логическое устройство

Арифметико-логическое устройство (АЛУ) — центральная часть процессора, выполняющая арифметические и логические операции.

На АЛУ выпадает самая важная роль в работе центрального процессора, «АЛУ выполняет сложение, вычитание и другие простые операции над входными данными и помещает результат в выходной регистр. Содержимое этого выходного регистра может записываться обратно в один из регистров или сохраняться в памяти, если это необходимо.» [2, c. 77]

В АЛУ существуют три базовые категории операций:

- логические операции, в которых реализуется построение логических операций И, ИЛИ, НЕ и пр.;

- арифметические операции, в которых результат деятельности данных операций, в виде базовых арифметических операций (умножения, деления, сложения и вычитания), и их аргументы представлены в виде чисел;

- операции над битами осуществляют побитовые сдвиги целых значений.

Команды АЛУ делится на две группы «команды типа регистр-память и типа регистр-регистр» [2, с. 77]:

«Команды первого типа вызывают слова из памяти, помещают их в регистры, где они используются в качестве входных данных АЛУ.» [2, с. 77]

«Команды второго типа вызывают два операнда из регистров, помещают их во входные регистры АЛУ, выполняют над ними какую-нибудь арифметическую или логическую операцию и переносят результат обратно в один из регистров. Этот процесс называется циклом тракта.» [2, c. 78]

Арифметико-логическое устройство содержит элемент управления выполняемым процессом, регистры и сумматор с подходящими логическими схемами. АЛУ действует в зависимости от передаваемого ему кода, который при отправлении данных необходимо выполнить для переменных, которые помещены в регистры.

Функционально АЛУ можно разделить на две группы:

- Первая содержит устройство управления, задающее последовательность выполняемых команд;

- Вторая содержит операционное устройство, реализующее заданную последовательность выполняемых команд.

Арифметико-логическое устройство оперирует 4 информационными типами элементов: булевскими (1 бит), числовыми (4 бита), байтными (8 бит) и адресными (16 бит). Также АЛУ выполняет 51 разнообразную операцию преобразования или отправки этих данных. Используя 11 режимов адресации, при помощи комбинирования, операции и режима адресации мы можем расширить базовое число команд до 255.

Также арифметико-логическое устройство содержит выходные индикационные сигналы: «Некоторые АЛУ имеют специальные выходные сигналы, называемые флагами, которые показывают информацию о выходе АЛУ. Например, флаг переполнения показывает, что результат работы сумматора переполнился. Флаг нуля показывает, что выход АЛУ установился на 0.» [4, c. 306]

2.2. Шина адреса и шина данных

Общепринято разделять вывод устройств по назначению: передача информации и передача сообщений всем устройствам, вывод, предназначенный для передачи информации, называется шиной данных.

Данная шина, располагаясь на материнской плате, обычно состоит из определённого количества параллельных проводников, принимающих данные от шины.

Главным показателем характеристики шины данных является объём бит передаваемых по всей ширине данной шины за один такт, что в свою очередь определяет какое количество данных может передавать шина за один такт.

Разрядность центрального процессора определяет разрядность самой шины данных.

Вывод, предназначенный для передачи сообщений всем устройствам, передающий адрес данных устройств, называется шиной адреса.

Данная шина используется центральным процессором, либо устройствами, которые могут инициировать сеансы прямого доступа к памяти, тем самым определяя физический адрес элемента оперативного запоминающего устройства (ОЗУ), к которому центральный процессор, либо определённое устройство стремится получить доступ, что бы в дальнейшем произвести операции записи, либо чтения.

Главным показателем характеристики шины адреса является, также как и в шине данных, объём бит передаваемых по всей ширине данной шины за один такт, тем самым определяя объём адресуемой памяти.

К примеру, рассматривая структурную схему микро-ЭВМ, команда, поступающая из центрального процессора, проходит по адресной шине и таким образом активизирует деятельность определённого устройства.

2.3 Регистр процессора

Регистр процессора — это, наиболее распространённый элемент последовательной логики, сверхбыстрая память внутри центрального процессора, которая специализирована на хранении временных данных центрального процессора, необходимых для дальнейших вычислений — смещения базовых таблиц, уровни доступа и т. д.

«Регистром называется набор из нескольких D-триггеров с общим тактовым сигналом». [4, с.160]

По сути, регистр — это цифровая электронная схема, предназначенная для хранения временных данных в виде двоичных чисел. Центральный процессор владеет большим количеством данных регистров, среди которых большая часть недоступна программистам и с которыми взаимодействует лишь самим центральным процессором, хотя существует определённый набор регистров, что доступны на программном уровне, но обратится к ним можно лишь из программной среды операционной системы.

В общем, польза регистра приведена в следующем: «Использование любого регистра по его прямому назначению сокращает длину объектного кода программы по сравнению с любым другим использованием регистра, так как использование регистра по назначению, как правило, предполагает его неявную адресацию». [6, c. 35]

Функционально, специализация регистров можно определить из их названий, приведём в пример наименования некоторых из них:

AX – Accumulator (регистра-аккумулятор) – по умолчанию используется для задания одного из операндов команды и для представления результата.

CX – Counter (счетчик) – по умолчанию используется, во-первых, как счетчик числа повторения циклов в команде «организация цикла» (LOOP); во-вторых, для задания числа сдвигов в командах сдвигов (его младший байт – CL); в-третьих, для задания числа элементов обрабатываемых строк (цепочек) в командах обработки строк (MOVS, CMPS и т.д.).

DX – Data (регистр данных) – по умолчанию используется как расширение аккумулятора со стороны старших разрядов в командах умножения и деления.

BX – Base (базовый регистр) – по умолчанию используется как базовая компонента эффективного адреса операнда, находящегося в памяти. (В терминологии фирмы Intel под эффективным адресом- Effective Address (EA) - понимается адрес операнда, формируемый программой (программный адрес).) Для получения физического адреса ячейки памяти, в которой находится операнд, осуществляется преобразование EA на основе простейшей модели сегментированной памяти (механизма сегментации).

SP - Stack Pointer (указатель стека) — по умолчанию используется для адресации вершины стека.

Поскольку регистры находятся на таком низком уровне доступа, доступ к их значениям, обычно, в несколько раз превосходит тот же доступ к данным оперативной памяти, но по сравнению с оперативной памятью суммарный объём всей памяти регистров намного меньше.

2.4 Счетчик команд

Большую часть ЭВМ, которые эксплуатируются по сей день, относят к неймановским вычислительным машинам, что подразумевает под собой то, что вычисления производятся на основе принципа, определённого Дж. Фон Нейманом, который называется принципом процедурного программирования.

Данный принцип характеризуется тем, что в центральном процессоре должно быть устройство управления, который содержит счётчик команд, для того «чтобы команды последовательно считывались и декодировались по заранее заданному в виде программы алгоритму вычислений, вычисления выполнялись в операционном устройстве и данные последовательно перезаписывались в запоминающее устройство» [7, c. 44]

Если, после выполнения команды, данная команда находится на своём месте в последовательности команд, то счётчик команд автоматически инкрементируется.

2.5 Кэш-память

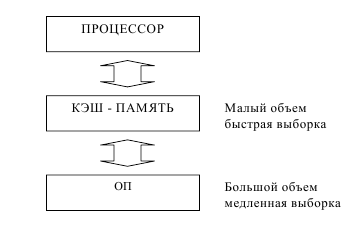

Кэш-память (англ. cache, от фр. cacher — прятать) – это «быстродействующая память, расположенная между центральным ЦП и основной памятью. Вместе с основной памятью она образует иерархическую структуру, и её действие эквивалентно быстрому доступу к основной памяти» [7, c. 51] Схема расположения кэш-памяти изображена на рисунке 1.

Рисунок 1 – Кэш-память

В кэш-памяти самая быстрая скорость доступа к данным.

Записать информацию в кэш-память возможно несколькими путями, которые называются «стратегией обновления основной памяти» [7, c. 52].

Стратегия обновления в кэш-памяти – это «метод (алгоритм), определяющий для заполненной кэш-памяти, какой из блоков следует возвратить в ОП для освобождения блока хэша с целью помещения в него блока ОП, к которому сейчас выполняется обращение.» [7, c. 53], помимо этого, бывают ещё различные стратегии замещения, в которых используется генератор случайных чисел, информация о наименьшей частоте использования блока, а также информация о временных параметрах обращения к блоку и метод прямого наложения блоков.

2.6 Кэш центрального процессора

Большое число моделей процессоров содержат собственный кэш, это необходимо для того, чтобы минимизировать доступ к оперативному запоминающему устройству.

Кэш-память даёт определённо значительный выигрыш в производительности, в случае, когда тактовая частота ОЗУ значительно меньше тактовой частоты ЦП. Тактовая частота для кэш-памяти обычно ненамного меньше частоты ЦП.

2.7 Уровни кэша

Кэш центрального процессора разделён на несколько уровней. Для универсальных процессоров — до 3. Кэш-память уровня N+1 как правило больше по размеру и медленнее по скорости обращения и передаче данных, чем кэш-память уровня N.

Самой быстрой памятью является кэш первого уровня — L1-cache. По сути, она является неотъемлемой частью процессора, поскольку расположена на одном с ним кристалле и входит в состав функциональных блоков. Состоит из кэша команд и кэша данных. Некоторые процессоры без L1 кэша не могут функционировать. На других его можно отключить, но тогда значительно падает производительность процессора. L1 кэш работает на частоте процессора, и, в общем случае, обращение к нему может производиться каждый такт (зачастую является возможным выполнять даже несколько чтений/записей одновременно). Латентность доступа обычно равна 2-4 тактам ядра. Объём обычно невелик — не более 128 Кбайт.

Вторым по быстродействию является L2-cache — кэш второго уровня. Обычно он расположен либо на кристалле, как и L1, либо в непосредственной близости от ядра, например, в процессорном картридже (только в слотовых процессорах). В старых процессорах — набор микросхем на системной плате. Объём L2 кэша от 128 Кбайт до 1-12 Мбайт. В современных многоядерных процессорах кэш второго уровня, находясь на том же кристалле, является памятью раздельного пользования — при общем объёме кэша в 8 Мбайт на каждое ядро приходится по 2 Мбайта. Обычно латентность L2 кэша, расположенного на кристалле ядра, составляет от 8 до 20 тактов ядра. В отличие от L1 кэша, его отключение может не повлиять на производительность системы. Однако, в задачах, связанных с многочисленными обращениями к ограниченной области памяти, например, СУБД, производительность может упасть в десятки раз.

Кэш третьего уровня наименее быстродействующий и обычно расположен отдельно от ядра ЦП, но он может быть очень внушительного размера — более 32 Мбайт. L3 кэш медленнее предыдущих кэшей, но всё равно значительно быстрее, чем оперативная память. В многопроцессорных системах находится в общем пользовании.

Отключение кэша второго и третьего уровней обычно используется в математических задачах, например, при обсчёте полигонов, когда объём данных меньше размера кэша. В этом случае, можно сразу записать все данные в кэш, а затем производить их обработку.

2.8 Классификация кэша

Кэш-память классифицируется по количеству строк в наборе.

Существует кэш прямого отображения, наборно-ассоциативный кэш и полностью ассоциативный кэш.

Уровень ассоциативности – это один из базовых характеристик кэш-памяти, который характеризует логическую сегментацию кэша.

Кэш прямого отображения – это кэш, в котором «каждый набор содержит только одну строку (один блок), так что кэш содержит S = B наборов» [4, с. 558], где S – это число наборов, а B – количество строк или блоков.

Для понимания принципа отображения адресов памяти в определённые строки данного кэша, можно представить, «что оперативная память поделена на блоки по b слов так же, как кэш поделен на строки по b слов. Адрес одного из слов, находящихся в блоке 0 оперативной памяти, отображается в набор 0 кэша. Адрес слова из блока 1 оперативной памяти отображается в набор 1 кэша, и так далее, пока адрес слова из блока B – 1 оперативной памяти не отобразится в строку B – 1 кэша. Больше строк в кэше нет, так что следующий блок оперативной памяти (блок В) снова отображается в строку 0 кэша, и так далее» [4, с. 559]

Наборно-ассоциативный кэш – это кэш, в котором «каждый набор состоит из N строк. Каждый адрес памяти по-прежнему отображается в один-единственный набор, но число наборов в этом случае равно S = B / N, а данные могут оказаться в любой из N строк этого набора» [4, с. 558]

Данного вида кэш уменьшает количество конфликтов, расширяя набор до N строк. Адреса памяти по-прежнему отображаются в строго установленной последовательности, но также теперь каждый адрес может быть отображён в любую из N строк данного набора. По сути, данный кэш – это «односекционный наборно-ассоциативный кэш.» [4, c. 563]

Полностью ассоциативный кэш – это кэш, который «имеет только один набор (S = 1), и данные могу оказаться в любой из B строк этого набора. Таким образом, полностью ассоциативный кэш – это то же самое, что и наборно-ассоциативный кэш с B секциями (количество секций совпадает с количеством строк во всём кэше).» [4, с. 558]

Для сравнения, при одинаковом объёме кэша, чем больше ассоциативность в кэше, тем он более медленный, но при этом более эффективный.

2.9 Математический сопроцессор

Сопроцессор – это специальный процессор, который увеличивается возможности ЦП, но реализованный в виде отдельного модуля.

Сопроцессор, предназначенный для процессоров без интегрированного модуля, увеличивающий множество команд центрального процессора, при этом обеспечивая его функционалом модуля операций с плавающей запятой, называют математическим сопроцессором.

Модуль операций с плавающей запятой (или с плавающей точкой; англ. floating point unit (FPU)) — часть процессора для выполнения широкого спектра математических операций над вещественными числами.

Простым «целочисленным» процессорам для работы с вещественными числами и математическими операциями требуются соответствующие процедуры поддержки и время для их выполнения. Модуль операций с плавающей запятой поддерживает работу с ними на уровне примитивов — загрузка, выгрузка вещественного числа (в/из специализированных регистров) или математическая операция над ними выполняется одной командой, за счёт этого достигается значительное ускорение таких операций.

ГЛАВА 3. АРХИТЕКТУРА ЦЕНТРАЛЬНОГО ПРОЦЕССОРА

Архитектура ЭВМ— это «многоуровневая иерархия аппаратно-программных средств, из которых строится ЭВМ. Каждый из уровнений допускается много вариантное построение и применение.» [7, c. 6] Понятие архитектуры ЭВМ является комплексным и включает в себя:

структурную схему ЭВМ;

средства и способы доступа к элементам структурной схемы;

организацию и разрядность интерфейсов ЭВМ;

набор и доступность регистров;

организацию и способы адресации памяти;

способы представления и форматы данных ЭВМ;

набор машинных команд ЭВМ;

форматы машинных команд;

обработку нештатных ситуаций (прерываний).

Архитектура центрального процессора— это «совокупность научных идей, структурных, организационных и технических решений, определяющих основные принципы функционирования процессора, его наблюдаемые характеристики и области практического применения.» [7, c. 6]

3.1 Архитектура фон Неймана

Большинство современных процессоров для персональных компьютеров в общем основаны на той или иной версии циклического процесса последовательной обработки информации, изобретённого Джоном фон Нейманом.

Д. фон Нейман придумал схему постройки компьютера в 1946 году.

Важнейшие этапы этого процесса приведены ниже. В различных архитектурах и для различных команд могут потребоваться дополнительные этапы. Например, для арифметических команд могут потребоваться дополнительные обращения к памяти, во время которых производится считывание операндов и запись результатов. Отличительной особенностью архитектуры фон Неймана является то, что инструкции и данные хранятся в одной и той же памяти.

Этапы цикла выполнения:

Процессор выставляет число, хранящееся в регистре счётчика команд, на шину адреса, и отдаёт памяти команду чтения;

Выставленное число является для памяти адресом; память, получив адрес и команду чтения, выставляет содержимое, хранящееся по этому адресу, на шину данных, и сообщает о готовности;

Процессор получает число с шины данных, интерпретирует его как команду (машинную инструкцию) из своей системы команд и исполняет её;

Если последняя команда не является командой перехода, процессор увеличивает на единицу (в предположении, что длина каждой команды равна единице) число, хранящееся в счётчике команд; в результате там образуется адрес следующей команды;

Данный цикл выполняется неизменно, и именно он называется процессом (откуда и произошло название устройства).

Во время процесса процессор считывает последовательность команд, содержащихся в памяти, и исполняет их. Такая последовательность команд называется программой и представляет алгоритм работы процессора. Очерёдность считывания команд изменяется в случае, если процессор считывает команду перехода — тогда адрес следующей команды может оказаться другим. Другим примером изменения процесса может служить случай получения команды останова или переключение в режим обработки прерывания.

Команды центрального процессора являются самым нижним уровнем управления компьютером, поэтому выполнение каждой команды неизбежно и безусловно. Не производится никакой проверки на допустимость выполняемых действий, в частности, не проверяется возможная потеря ценных данных. Чтобы компьютер выполнял только допустимые действия, команды должны быть соответствующим образом организованы в виде необходимой программы.

3.2 Конвейерная архитектура

Общая идея конвейера связана с разбиением некоторого процесса обработки объектов на независимые этапы и организацией параллельного выполнения во времени различных этапов обработки различных объектов, передвигающихся по конвейеру от одного этапа к другому. Поэтому основой разработки конвейера является разбиение процесса на независимые этапы. Рассмотрим такое разбиение на примере машинной команды умножения чисел с плавающей точкой.

Конвейерная архитектура (pipelining) была введена в центральный процессор с целью повышения быстродействия. Обычно для выполнения каждой команды требуется осуществить некоторое количество однотипных операций, например: выборка команды из ОЗУ, дешифрация команды, адресация операнда в ОЗУ, выборка операнда из ОЗУ, выполнение команды, запись результата в ОЗУ. Каждую из этих операций сопоставляют одной ступени конвейера. Например, конвейер микропроцессора с архитектурой MIPS-I содержит четыре стадии:

- получение и декодирование инструкции (Fetch)

- адресация и выборка операнда из ОЗУ (Memory access)

- выполнение арифметических операций (Arithmetic Operation)

- сохранение результата операции (Store)

После освобождения k-й ступени конвейера она сразу приступает к работе над следующей командой. Если предположить, что каждая ступень конвейера тратит единицу времени на свою работу, то выполнение команды на конвейере длиной в n ступеней займёт n единиц времени, однако в самом оптимистичном случае результат выполнения каждой следующей команды будет получаться через каждую единицу времени.

Действительно, при отсутствии конвейера выполнение команды займёт n единиц времени (так как для выполнения команды по-прежнему необходимо выполнять выборку, дешифрацию и т. д.), и для исполнения m команд понадобится единиц времени; при использовании конвейера (в самом оптимистичном случае) для выполнения m команд понадобится всего лишь n + m единиц времени.

Факторы, снижающие эффективность конвейера:

простой конвейера, когда некоторые ступени не используются (напр., адресация и выборка операнда из ОЗУ не нужны, если команда работает с регистрами);

ожидание: если следующая команда использует результат предыдущей, то последняя не может начать выполняться до выполнения первой (это преодолевается при использовании внеочередного выполнения команд, out-of-order execution);

очистка конвейера при попадании в него команды перехода (эту проблему удаётся сгладить, используя предсказание переходов).

Некоторые современные процессоры имеют более 30 ступеней в конвейере, что увеличивает производительность процессора, однако приводит к большому времени простоя (например, в случае ошибки в предсказании условного перехода.)

3.3 Суперскалярная архитектура

Способность выполнения нескольких машинных инструкций за один такт процессора. Появление этой технологии привело к существенному увеличению производительности.

3.4 CISC-процессоры

Complex Instruction Set Computer — вычисления со сложным набором команд. Процессорная архитектура, основанная на усложнённом наборе команд. Типичными представителями CISC является семейство микропроцессоров Intel x86 (хотя уже много лет эти процессоры являются CISC только по внешней системе команд).

3.5 RISC-процессоры

Для быстрого выполнения программы, написанной на языке высокого уровня, не нужны сложные машинные команды - гораздо более важно сократить время выполнения наиболее часто используемых команд. Этот принцип был положен в основу RISC-архитектуры, которая представляет собой улучшенный вариант неймановской архитектуры. Благодаря сокращению набора команд упрощаются аппаратные схемы, а значит, обеспечивается оптимизация выполнения часто используемых команд. Кроме того, за счет применения большого числа регистров уменьшается частота (число) доступов к памяти, что также позволяет повысить скорость выполнения команды.

Reduced Instruction Set Computer — вычисления с сокращённым набором команд. Архитектура процессоров, построенная на основе сокращённого набора команд. Характеризуется наличием команд фиксированной длины, большого количества регистров, операций типа регистр-регистр, а также отсутствием косвенной адресации. Концепция RISC разработана Джоном Коком (John Cocke) из IBM Research, название придумано Дэвидом Паттерсоном (David Patterson).

Среди первых реализаций этой архитектуры были процессоры MIPS, PowerPC, SPARC, Alpha, PA-RISC. В мобильных устройствах широко используются ARM-процессоры.

3.6 MISC-процессоры

Minimum Instruction Set Computer — вычисления с минимальным набором команд. Дальнейшее развитие идей команды Чака Мура, который полагает, что принцип простоты, изначальный для RISC-процессоров, слишком быстро отошёл на задний план. В пылу борьбы за максимальное быстродействие, RISC догнал и перегнал многие CISC процессоры по сложности. Архитектура MISC строится на стековой вычислительной модели с ограниченным числом команд (примерно 20-30 команд).

3.7 Параллельная архитектура

Архитектура фон Неймана обладает тем недостатком, что она последовательная. Какой бы огромный массив данных ни требовалось обработать, каждый его байт должен будет пройти через центральный процессор, даже если над всеми байтами требуется провести одну и ту же операцию. Этот эффект называется узким горлышком фон Неймана.

Для преодоления этого недостатка предлагались и предлагаются архитектуры процессоров, которые называются параллельными. Параллельные процессоры используются в суперкомпьютерах.

Возможными вариантами параллельной архитектуры могут служить (по классификации Флинна):

SISD — один поток команд, один поток данных;

SIMD — один поток команд, много потоков данных;

MISD — много потоков команд, один поток данных;

MIMD — много потоков команд, много потоков данных

ГЛАВА 4. ФУНКЦИИ ЦЕНТРАЛЬНОГО ПРОЦЕССОРА

Центральный процессор выполняет очень важную функцию в компьютере, поэтому от его мощности зависит корректность и скорость выполнения работы остальных компонентов компьютера. Например, при недостаточной мощности центрального процессора, программа не может стабильно просчитываться, что в свою очередь сказывается, например, на видеокарте, которая может в последствии не корректно себя проявить.

Когда логика программы доходит до процессора, то её выполнение неизбежно, т.к. команды, выполняемые на данном этапе находятся в самом нижайшем уровне управления, т.е., иначе говоря, на самом базовом, из возможных, уровне выполнения программы. На данном уровне невозможно перехватить на корректность выполнения или же возможность утери данных, команда выполняется по принципу «как есть», поэтому для устранения огромного количества проблем, необходимо создавать корректно организованные программы с учётом большинства возможных рисков.

Каждый цикл выполнения команды центральным процессором выполняется с определённой скоростью, которая задаётся тактовым генератором. Данный генератор, в свою очередь, задаёт равную последовательность импульсов с определённой частой, которая называется – тактовой частотой.

В общем случае основными функциями центрального процессора являются:

- выборка (чтение) выполняемых инструкций. Каждая команда сохраняется в памяти и имеет свой собственный адрес. Процессор запоминает этот адрес из программного счетчика, который отвечает за отслеживание того, какую инструкцию ЦП должен выполнить следующей.

- декодирование кода - все программы, которые должны быть выполнены, будут переведены на язык Ассемблер. Код Ассемблера выполнен в бинарных инструкциях, которые понятны процессору. Этот шаг называется декодированием.;

- вывод (чтение) данных из памяти или устройства ввода/вывода;

- ввод (запись) данных в память или устройство ввода/вывода;

- обработка данных (операндов), в том числе арифметические операции над ними;

- адресация памяти, то есть задание логического адреса памяти, с которым будет производиться обмен;

- обработка прерываний и режима прямого доступа;

- Выполнение. При выполнении инструкции, процессор может сделать одно из трех действий: передать инструкцию в АЛУ (арифметико-логическое устройство), переместить данные из одного места памяти в другое, или перейти к другому адресу;

- Исполнение. Процессор должен передать результаты после выполнения инструкции, эти выходные данные записываются в память.

Но если представить функции центрального процессора максимально абстрактно, то мы получим две обобщённые функции центрального процессора:

- обрабатывание данных выполняемой программы, выполняя логические и арифметические операции;

- управление деятельностью hardware-компонентов компьютера из программной среды.

Когда центральный процессор получает инструкцию от устройств, отвечающих за ввод или вывод, центральный процессор декодирует код, отвечающий за выполнение, и выводит данные на экран.

Свои функции центральный процессор выполняет ежесекундно, обеспечивания корректное и стабильное выполнение своих функций компьютером.

ГЛАВА 5. КЛАССИФИКАЦИЯ

Процессоры классифицируются числу больших интегральных схем, по назначению, по виду обрабатываемых сигналов, по количеству выполняемых программ, по характеру временной организации и по объёму набора инструкций.

По количеству больших интегральных схем бывают процессоры однокристальные, в которых весь процессор расположен на одном кремниевом кристалле в схеме, и многокристальные, в которых различные блоки центрального процессора расположены на различных кристаллах.

По назначению центральные процессоры делятся на универсальные процессоры, которые можно, без особого влияния на производительность, применить для решения обширного спектра задач любой специфики, и специализированные процессоры, которые предназначены для выполнения трудоёмких задач в виде ряда логических операций.

По виду обрабатываемых сигналов центральные процессоры реализуются в виде цифровых, работающих с дискретными значениями, и аналоговые, которые специализированы на обработке аналогово сигнала.

По количеству выполняемых программ бывают однопрограммные, специализированные на решении только единственной задачи, также существуют многопрограммные процессоры, выполняющие одновременно определённое количество программ.

По характеру временной организации работы существуют синхронные процессоры, они характеризуются тем, что выполняемые операции регулируются устройством управления, также, соответственно, существуют асинхронные процессоры, в которых регулирование выполнения зависит от реального завершения выполнения предыдущей задачи.

По объёму набора инструкций бывают процессоры с полным набором инструкций (CISC) и процессоры с сокращенным набором инструкций.

ЗАКЛЮЧЕНИЕ

Центральный процессор – это неотъемлемая часть современных компьютеров, без которой не мыслима их деятельность, т.к. все вычисления в программе «процессируют» через процессор.

В данной курсовой работе рассматривается структурный состав, архитектура, функции, а также классификации центрального процессора.

В первой главе даны определения центрального процессора и его составляющих, а также был обобщённо описан центральный процессор.

Во второй главе рассмотрен структурный состав центрального процессора, а в частности: арифметико-логическое устройство (АЛУ), шина адреса и шина данных, регистры процессора, счетчики команд, кэш-память, кэш центрального процессора, уровни кэша, классификация кэша и математический сопроцессор чисел с плавающей точкой.

В третьей главе рассмотрена архитектура центрального процессора, а частности: архитектура фон Неймана, конвейерная архитектура, суперскалярная архитектура, CISC-процессоры, RISC-процессоры, MISC-процессоры и параллельная архитектура.

В четвёртой главе рассмотрены основные функции центрального процессора.

В пятой главе рассмотрены классификации центрального процессора.

На основе проведённой работы, можно сделать вывод о том, что центральный процессор компьютера играет огромную роль в жизни человеческого общества, так как без центрального процессора не может функционировать компьютер, а без компьютера уже невозможно представить огромное множество видов деятельности современного человеческого общества.

БИБЛИОГРАФИЯ

- ГОСТ 15971-90 Системы обработки информации. Термины и определения: утвержден и введен в действие Постановлением Государственного комитета СССР по управлению качеством продукции и стандартам от 26.10.90 N 2698

- Таннебаум Э. Архитектура компьютера. 6-е изд./ Э. Таннебаум, Т. Остин. – СПб.: Питер, 2013. – 816 с.

- Паттерсон Д. Архитектура компьютера и проектирование компьютерных систем. 4-е изд./ Д. Паттерсон, Д. Хеннесси. – СПб.: Питер, 2012. – 784 с.

- Харрис Д. Цифровая схемотехника и архитектура компьютера. / Д.М. Харрис, С.Л. Харрис. – М.: ДМК Пресс, 2018. – 792 с.

- Брайант Р. Компьютерные системы: архитектура и программирование. Взгляд программиста. / Р. Брайант, Д. О'Халларон. – СПб.: БХВ-Петербург, 2005. – 1090 с.

- Довгий П.С. Прикладная архитектура базовой модели процессора Intel. Учебное пособие по дисциплине «Организация ЭВМ и систем». / П.С. Довгий, В.И. Поляков – СПб.: НИУ ИТМО, 2012. – 115 с.

- Ульянов М.В. Архитектуры процессоров. / М.В. Ульянов. – М.: МГАПИ, 2002. – 68 с.

- Эволюция форм и видов денег (Экономическая роль денег и ступени их развития)

- Социальное страхование как элемент социальной защиты в современной России

- Понятие и классификация функций государства (Виды функций государства)

- Учет поступления основных средств (Исследование нормативной базы по учету основных средств)

- Учет поступления основных средств (Особенности деятельности предприятия и его учетная политика)

- Учет труда и заработной платы ( Понятие "заработная плата")

- Публичная власть. Особенности публичной власти в Российской Федерации

- Использование типологии трудовой мотивации менеджеров и сотрудников по В. Герчикову в современной организации

- Сущность оптовых ярмарок, их функции и роль в системе товароснабжения ( Теоретические аспекты изучения организации закупок на оптовых ярмарках )

- азработка системы тестирования обучающихся в ГБПОУ колледж «Царицыно»

- Процессы принятия решений в организации (Оценка общей эффективности комплекса исторически принятых решений)

- Формы государственного устройства ( Понятие формы государства )