Классификация, структура и основные характеристики современных микропроцессоров ПК.

Содержание:

ВВЕДЕНИЕ

В современном мире трудно найти область техники, где не применялись бы микропроцессоры. Они применяются при вычислениях, они выполняют функции управления, они используются при обработке звука и изображения. Сейчас даже более-менее продвинутые мобильные телефоны не обходятся без микропроцессора, что уже говорить о планшетных, переносных и настольных персональных компьютерах. Что же такое микропроцессор и как развивалась история его создания? Если говорить на понятном языке, то микропроцессор – это более сложная и многофункциональная интегральная схема.

История микросхемы (интегральной схемы) начинается с 1958 года, когда сотрудник американской фирмы Texas Instruments Джек Килби изобрел некое полупроводниковое устройство, содержащее в одном корпусе несколько транзисторов, соединенных между собой проводниками. Первая микросхема – прародительница микропроцессора – содержала всего лишь 6 транзисторов и представляла собой тонкую пластину из германия с нанесёнными на неё дорожками, выполненными из золота, Расположено всё это было на стеклянной подложке. Для сравнения, сегодня счет идет на единицы и даже десятки миллионов полупроводниковых элементов.

К 1970 году достаточно много производителей занималось разработкой и созданием интегральных схем различной емкости и разной функциональной направленности. Но именно этот год можно считать датой рождения первого микропроцессора. Именно в этом году фирма Intel создает микросхему памяти емкостью всего лишь 1 Кбит – ничтожно мало для современных процессоров, но невероятно велико для того времени. На то время это было огромнейшее достижение – микросхема памяти способна была хранить до 128 байт информации – намного выше подобных аналогов. Кроме этого примерно в тоже время японский производитель калькуляторов Busicom заказала той же Intel 12 микросхем различной функциональной направленности. Специалистам Intel удалось реализовать все 12 функциональных направленностей в одной микросхеме. Более того, созданная микросхема оказалась многофункциональной, поскольку позволяла программно менять свои функции, не меняя при этом физической структуры. Микросхема выполняла определенные функции в зависимости от подаваемых на ее управляющие выводы команд.

Уже через год в 1971 Intel выпускает первый 4-разрядный микропроцессор под кодовым именем 4004. По сравнению с первой микросхемой в 6 транзисторов, он содержал 2,3 тыс. полупроводниковых элементов и выполнял 60 тыс. операций в секунду. На то время – это был огромнейший прорыв в области микроэлектроники. 4-разрядный означало то, что 4004 мог обрабатывать сразу 4-х битные данные. Еще через два года в 1973 фирма выпускает 8-ми разрядный процессор 8008, который работал уже с 8-ми битными данными. Начиная с 1976 года, компания начинает разрабатывать уже 16-разрадную версию микропроцессора 8086. Именно он начал применяться в первых персональных компьютерах IBM и, по сути, заложил один из кирпичиков в историю ЭВМ.

Наиболее важными компонентами любого компьютера, обуславливающими его основные характеристики, являются микропроцессоры, системные платы и интерфейсы.

Микропроцессор (МП), или Central Processing Unit (CPU) — функционально-законченное программно управляемое устройство обработки информации, выполненное в виде одной или нескольких больших (БИС) или сверхбольших (СБИС) интегральных схем.

Глава 1. Микропроцессоры.

1.1. Функции микропроцессора

Микропроцессор выполняет следующие функции:

- вычисление адресов команд и операндов;

- выборку и дешифрацию команд из основной памяти (ОП);

- выборку данных из ОП, регистров МПП и регистров адаптеров внешних устройств (ВУ);

- прием и обработку запросов и команд от адаптеров на обслуживание ВУ;

- обработку данных и их запись в ОП, регистры МПП и регистры адаптеров ВУ;

- выработку управляющих сигналов для всех прочих узлов и блоков ПК;

- переход к следующей команде.

1.2. Параметры микропроцессоров

Основными параметрами микропроцессоров являются:

- разрядность;

- рабочая тактовая частота;

- виды и размер кэш-памяти;

- состав инструкций;

- конструктив;

- рабочее напряжение и т. д.

Разрядность шины данных микропроцессора определяет количество разрядов, над которыми одновременно могут выполняться операции; разрядность шины адреса МП определяет его адресное пространство.

Адресное пространство — это максимальное количество ячеек основной памяти, которое может быть непосредственно адресовано микропроцессором.

Рабочая тактовая частота МП во многом определяет его внутреннее быстродействие, поскольку каждая команда выполняется за определенное количество тактов. Быстродействие (производительность) ПК зависит также и от тактовой частоты шины системной платы, с которой работает (может работать) МП.

Кэш-память, устанавливаемая на плате МП, имеет два уровня:

- L1 — память 1-го уровня, находящаяся внутри основной микросхемы (ядра) МП и работающая всегда на полной частоте МП (впервые кэш L1 был введен в МП i486 и у МП i386SLC);

- L2 — память 2-го уровня, кристалл, размещаемый на плате МП и связанный с ядром внутренней микропроцессорной шиной (впервые введен в МП Pentium II). Память L2 может работать на полной или половинной частоте МП. Эффективность этой кэш-памяти зависит и от пропускной способности микропроцессорной шины.

Состав инструкций — перечень, вид и тип команд, автоматически исполняемых МП. От типа команд зависит классификационная группа МП (CISC, RISC, VLIW и т. д.). Перечень и вид команд определяют непосредственно те процедуры, которые могут выполняться над данными в МП, и те категории данных, над которыми применимы эти процедуры. Дополнительные инструкции в небольших количествах вводились во многих МП (286, 486, Pentium Pro и т. д.). Но существенное изменение состава инструкций произошло в МП i386 (этот состав далее принят за базовый), Pentium MMX, Pentium III, Pentium 4, Pentium D, Core Duo.

Конструктив подразумевает те физические разъемные соединения, в которые устанавливается МП, и которые определяют пригодность материнской платы для установки МП. Разные разъемы имеют разную конструкцию (Slot — щелевой разъем, Socket — разъем-гнездо), разное количество контактов, на которые подаются различные сигналы и рабочие напряжения.

Рабочее напряжение также является фактором пригодности материнской платы для установки МП.

1.3. Классификация микропроцессоров

В настоящее время разными фирмами (AMD, VIA Apollo, IBM и др.) выпускается много десятков различных микропроцессоров, но наиболее популярными и распространенными являются микропроцессоры фирмы Intel и Intel-подобные.

Все микропроцессоры можно разделить на группы:

- CISC (Complex Instruction Set Command) с полным набором системы команд;

- RISC (Reduced Instruction Set Command) с усеченным набором системы команд;

- VLIW (Very Length Instruction Word) со сверхдлинным командным словом;

- MISC (Minimum Instruction Set Command) с минимальным набором системы команд и весьма высоким быстродействием.

1.3.1 Микропроцессоры типа CISC

Большинство современных ПК типа IBM PC используют МП типа CISC, выпускаемые многими фирмами: Intel, AMD, Cyrix, IBM и т. д. Законодателем «мод» здесь выступает Intel, но ей «на пятки» наступает AMD, в последние годы создавшая МП по некоторым параметрам лучше «интеловских». Все же пока МП фирмы Intel имеют большее распространение; характеристики некоторых из них приведены в таблице 1.

Таблица 1. Характеристики некоторых CISC МП

|

Модель МП Intel |

Разрядность данных/адреса (бит) |

Тактовая частота (МГц) |

Адресное пространство (байт) |

Состав команд |

Число элементов; Технология |

Кэш L1 и L2 (кБайт) |

Напряжения питания; Конструктив |

Годы выпуска |

|

|

4004 |

4 |

4 |

0,108 |

4103 |

2300; 10 мкм |

1971 |

|||

|

8080 |

8 |

8 |

2,0 |

64103 |

10 000; 6 мкм |

1974 |

|||

|

8066 |

16 |

16 |

4,77 и 8 |

106 |

70 000;3 мкм |

1979 |

|||

|

8088 |

8, 16 |

16 |

4,77 и 8 |

106 |

70 000;3 мкм |

1978 |

|||

|

80186 |

16 |

20 |

8 и 10 |

106 |

140 000 |

1981 |

|||

|

80286 |

16 |

24 |

8-20 |

16106 |

180 000; 1,5 мкм |

1982 |

|||

|

80386 |

32 |

32 |

16-50 |

4109 |

Базовый |

275 000; 1 мкм |

1985 |

||

|

80486 |

32 |

32 |

25-100 |

4109 |

Базовый |

1,2106; 1 мкм |

8 |

1989 |

|

|

Pentium |

64 |

32 |

60-233 |

4109 |

Базовый |

3,3106; 0,5, 0,35 мкм |

8+8 |

5 B; Socket 5 |

1993 |

|

Pentium Pro |

64 |

32 |

150-200 |

4109 |

Базовый |

5,5106; 0,5, 0,35 мкм |

8+8 |

5 B; Socket 8 |

1995 |

|

Pentium MMX |

64 |

36 |

166-233 |

64109 |

Базовый + 57 (MMX) |

5106; 0,35 мкм |

16+16 |

2,8 B; Socket 7 |

1997 |

|

Pentium II (Katmai) |

64 |

36 |

233-600 |

64109 |

MMX + (MMX2) |

7,5106; 0,25 мкм |

16+16 512F/2 |

2,0 B; Slot 1 |

1997 |

|

Intel Celeron (Mendocino) |

64 |

32 |

300-800 |

4109 |

MMX2 |

19106; 0,25, 0,22 мкм |

16+16 128F |

2,0 B; Slot 1, Socket 370 |

1998 |

|

Pentium III (Coppermine) |

64 |

36 |

500-1000 |

64109 |

MMX + 70 |

28106; 0,18 мкм |

16+16 256F |

1,65 B; Slot 1, Socket 370 |

1999 |

|

Intel Pentium III Xeon |

64 |

36 |

500-1000 |

64109 |

MMX2 |

30106; 0,18, 0,13 мкм |

16+16 256-2048F |

1,65 B; Slot 2 |

1999 |

|

Pentium 4 (Willarmette) |

64 |

36 |

1000-3500 |

64109 |

MMX2 + 144 |

42106; 0,13 мкм |

8+8 256F |

1,1-1,85 B; Socket 423, 478 |

2000 |

|

Pentium 4 XE (Gallatine) |

64 |

36 |

3200-3600 |

10649 |

SSE3 |

101786; 0,09мкм |

16+16 2048F |

Socket LGA 775; Strained, SOI, Cu |

2004 |

|

Pentium D 2 ядра |

64 |

64 |

2800-3200 |

10649 |

SSE3+ |

102756; 0,09мкм |

16+16 1024x2 |

Socket LGA 775, Strained, SOI, Cu |

2005 |

Условные обозначения в столбце «Состав команд»: «ММХ +» означает, что имеется несколько дополнительных 32-битовых инструкций группы SSE (Streaming SIMD Extention). В столбце кэш символ F у кэш-памяти уровня L2 означает, что память работает на частоте процессора; обозначение F/2 — на половинной частоте процессора.

Пояснения к таблице:

- число элементов — это количество элементарных полупроводниковых переходов, размещенное в интегральной схеме МП. Технология обычно характеризуется размером элемента в микронах (микронная технология).

- микропроцессоры 80486DX и выше имеют встроенный математический сопроцессор, могут работать с умножением внутренней частоты. С увеличенной частотой работают только внутренние схемы МП, все внешние по отношению к МП схемы, в том числе расположенные и на системной плате, работают с обычной частотой;

- у МП 80286 и выше конвейерное выполнение команд — это одновременное выполнение разных тактов последовательных команд в разных частях МП при непосредственной передаче результатов из одной части МП в другую, увеличивает эффективное быстродействие ПК в 2-5 раз;

- у МП 80286 и выше есть возможность работы в вычислительной сети;

- у МП 80286 и выше имеется возможность многозадачной работы (многопрограммность) и сопутствующая ей защита памяти.

Современные микропроцессоры имеют два режима работы:

Реальный (однозадачный, Real Address Mode), в котором возможно выполнение только одной программы и непосредственно адресоваться могут только 1024 + 64 Кбайт основной памяти компьютера, а остальная память (расширенная) доступна лишь при подключении специальных драйверов;

Защищенный (многозадачный, Protected Virtual Address Mode), обеспечивающий выполнение сразу нескольких программ, непосредственную адресацию и прямой доступ (без дополнительных драйверов) к расширенной основной памяти. Предоставляется непосредственный доступ к памяти емкостью 16 Мбайт для МП 286; 4 Гбайт для процессоров 386, 486, Celeron; 100 Гбайт для МП Pentium Xeon и 64 Гбайт для остальных процессоров Pentium, а при страничной организации памяти — к 16 Тбайт виртуальной памяти для каждой задачи. В этом режиме осуществляется автоматическое распределение памяти между выполняемыми программами и соответствующая ее защита от обращений со стороны чужих программ. Защищенный режим поддерживается операционными системами Windows, OS/2, UNIX и т. д.

- в МП 80386 и выше встроена поддержка системы виртуальных машин. Система виртуальных машин является дальнейшим развитием режима многозадачной работы, при котором каждая задача может выполняться под управлением своей операционной системы, то есть практически в одном МП моделируется как бы несколько компьютеров, работающих параллельно и имеющих разные операционные системы;

- у МП 80486 и выше имеется поддержка кэш-памяти;

- у МП 80486 и выше имеются RISC-элементы, позволяющие выполнять короткие операции за 1 такт.

Микропроцессоры 80586 (Р5) более известны по их товарной марке Pentium, которая запатентована фирмой Intel (МП 80586 других фирм имеют иные обозначения: К5 у фирмы AMD, Ml у фирмы Cyrix и т. д.).

МП шестого поколения 80686 (Р6), торговая марка Pentium Pro, имеют более высокую производительность благодаря наличию «динамического исполнения» (dynamic execution).

Это означает:

- наличие многоступенчатой суперконвейерной структуры (superpipelining),

- наличие предсказания ветвлений программы при условных передачах управления (multiple branch prediction)

- исполнение команд по предполагаемому пути ветвления (speculative execution).

В программах решения многих задач содержится большое число условных передач управления. Если процессор может заранее предсказывать направление перехода (ветвления), то производительность его работы значительно повысится за счет оптимизации загрузки вычислительных конвейеров. Если путь ветвления предсказан неверно, процессор должен сбросить полученные результаты, очистить конвейеры и загрузить нужные команды заново, что требует достаточно большого числа тактов. В процессоре Pentium Pro вероятность правильного предсказания 90%, против 80% у МП Pentium.

МП Pentium ММХ (ММХ — MultiMedia eXtention) и Pentium II модернизированы для работы в мультимедийной технологии. В них появилась качественно новая технология: начали внедряться инструкции SIMD (Single Instruction Multiply Data), в которых одно и то же действие совершается над многими данными. Более дешевый вариант Pentium II – Celeron (с отсутствующим либо урезанным до 128 Кбайт кэшем 2-го уровня).

В МП Pentium III присутствует новый блок 128-разрядных регистров, что позволило осуществить расширение набора SIMD-инструкций, ориентированных на форматы данных с плавающей запятой — SSE (Streaming SIMD Extensions). Увеличен кэш 2-го уровня. Pentium III Xeon — процессоры, позиционированные для серверов.

В Pentium 4 улучшена система «динамического исполнения».

Динамическое исполнение позволяет процессору предсказывать порядок выполнения инструкций при помощи технологии множественного предсказания ветвлений, которая прогнозирует прохождение программы по нескольким ветвям. Это оказывается возможным, поскольку в процессе исполнения инструкции процессор просматривает программу на несколько шагов вперед. Технология анализа потока данных позволяет проанализировать программу и составить ожидаемую последовательность исполнения инструкций независимо от порядка их следования в тексте программы. И, наконец, опережающее выполнение повышает скорость работы программы за счет выполнения нескольких инструкций одновременно, по мере их поступления в ожидаемой последовательности — то есть по предположению (интеллектуально). Поскольку выполнение инструкций происходит на основе предсказания ветвлений, результаты сохраняются как «интеллектуальные» с последующим удалением тех, которые вызваны промахами в предсказании. На конечном этапе порядок инструкций и результатов их выполнения восстанавливается до первоначального.

Технология ускоренных вычислений использует два быстрых АЛУ, выполняющие короткие арифметические и логические операции, и третье медленное АЛУ, исполняющее длинные операции (умножение, деление и т. д.).

Используется технология Hyper Treading (tread- поток) – на базе одного МП формируются 2 или более логических процессоров, работающих параллельно. Для задач, позволяющих распараллеливать операции, производительность МП повышается на 30 %.

По мнению специалистов, повышение быстродействия МП путем увеличения тактовой частоты их работы исчерпало себя. Поэтому производительность было решено увеличивать за счет параллельного выполнения вычислений. Появляются многоядерные МП.

Первым представителем двухъядерных МП для ПК в 2005 году стал Pentium D.

Двухъядерные МП по сравнению с параллельными виртуальными процессорами обеспечивают существенно большую производительность, т. к. у них почти нет совместно используемых процессорных ресурсов (АЛУ, МПП, кэш-память L1 у каждого свои). Потребляемая мощность у них значительно меньше, чем у более высокочастотных однопроцессорных МП той же производительности. Поэтому двух- и многоядерные МП активно используются в ПК. Для двухъядерных МП необходимы системные платы со специальными разъемами и чипсетами.

В феврале 2005 г. компаниями Sony, Toshiba и IBM представлены девятиядерные МП Cell (ячейка). В них используется 0,09 мкм-технология, а также достижения электроники: «кремний на изоляторе» (SOI), «напряженный кремний» (StrainedSi), медные соединения (Cu). Имеют очень низкое энергопотребление (до 80 Вт).

В 2006 г. Intel представила линейку МП Core:

Core Solo (1 ядро),

Core Duo, Core 2 Duo, Core 2 Extreme (2 ядра),

Core 2 Quad (4 ядра),

Core Penryn (2-4 ядра).

Все МП этой линейки строятся по 65-нанометровой технологии, используют ряд новых энергосберегающих технологий.

В 2008 г. Intel предложила 0,045-микронную архитектуру Nechalem– она использует при построении МП модульность, которая позволяет варьировать количество ядер в МП и изменять насыщенность процессорной системы прочими блоками, в зависимости от назначения и требуемой производительности.

Используют эту архитектуру МП Core i5 и Core i7. Core i5 является несколько облегченным вариантом Core i7. МП Core i3 — по уровню цены и производительности стоят на самой низкой ступени, перед более дорогими и производительными Core i5. В таблице 2 приведены характеристики микропроцессоров Intel.

Таблица 2. Характеристики МП Intel.

|

Модель |

Ядро |

Тактовая частота, ГГц |

Цена |

Рассеиваемая мощность, Вт |

Частота видеоядра, МГц |

Дата выпуска |

|

Модель Core i3 |

||||||

|

540 |

Clarkdale 2 ядра |

3,06 |

$133 |

73 |

733 |

янв. 2010 |

|

530 |

Clarkdale 2 ядра |

2,93 |

$113 |

73 |

733 |

янв. 2010 |

|

Модель Core i5 |

||||||

|

750 |

Lynnfield 4 ядра |

2,66 (3,2) |

$196 |

95 |

отсутствует |

сен. 2009 |

|

670 |

Clarkdale 2 ядра |

3,46 (3,73) |

$284 |

73 |

733 |

янв. 2010 |

|

661 |

3,33 (3,6) |

$196 |

87 |

900 |

янв. 2010 |

|

|

660 |

3,33 (3,6) |

$196 |

73 |

733 |

янв. 2010 |

|

|

650 |

3,2 (3,46) |

$176 |

73 |

733 |

янв. 2010 |

|

|

Модель Core i7 |

||||||

|

860 |

Lynnfield 4 ядра |

2,80 |

$284 |

95 |

сен. 2009 |

|

|

870 |

Lynnfield 4 ядра |

2.93 |

$562 |

95 |

сен. 2009 |

1.3.2 Микропроцессоры типа RISC

Микропроцессоры типа RISC содержат только набор простых, чаще всего встречающихся в программах команд. При необходимости выполнения более сложных команд в микропроцессоре производится их автоматическая сборка из простых. В этих МП все простые команды имеют одинаковый размер и на выполнение каждой из них тратится 1 машинный такт (на выполнение даже самой короткой команды из системы CISC обычно тратится 4 такта).

Современные 64-разрядные RISC-микропроцессоры выпускаются многими фирмами: Apple (PowerPC), IBM (PPC), DEC (Alpha), HP (PA), Sun (Ultra SPARC) и т. д.

Микропроцессоры типа RISC характеризуются очень высоким быстродействием, но они программно не совместимы с CISC-процессорами: при выполнении программ, разработанных для ПК типа IBM PC, они могут лишь эмулировать (моделировать, имитировать) МП типа CISC на программном уровне, что приводит к резкому уменьшению их эффективной производительности.

1.3.3 Микропроцессоры типа VLIW

Это новый и весьма перспективный тип МП. Микропроцессоры типа VLIW выпускают фирмы Transmeta — это микропроцессор Crusoe моделей ТМ3120, ТМ5400, ТМ5600, Intel — модель Mersed (торговая марка Itanium) и Hewlett-Packard — модель McKinley.

К VLIW-типу можно отнести и МП Elbrus 2000 — E2k, разработанный российской компанией «Эльбрус».

Программисты доступа к внутренним VLIW-командам не имеют: все программы (даже операционная система) работают поверх специального низкоуровневого программного обеспечения (Code Morphing), которое ответственно за трансляцию команд CISC-микропроцессоров в команды VLIW. МП типа VLIW вместо сложной схемной логики, обеспечивающей в современных суперскалярных микропроцессорах параллельное исполнение команд, опираются на программное обеспечение. Упрощение аппаратуры позволило уменьшить габариты МП и потребление энергии (эти МП иногда называют «холодными»).

1.4. Физическая и функциональная структура микропроцессора

В состав микропроцессора Pentium обычно входят следующие физические компоненты:

- Core — ядро МП;

- Execution Unit — исполняющий модуль;

- IntegerALU— АЛУ для операций с целыми числами (с фиксированной запятой);

- Registers — регистры;

- Floating Point Unit — блок для работы с числами с плавающей запятой;

- Primary Cache — кэш первого уровня, в том числе кэш данных (Data Cache) и кэш команд (Code Cache);

- Instruction Decode and Prefetch Unit и Branch Predictor — блоки декодирования инструкций, опережающего их исполнения и предсказания ветвлений;

- Bus Interface — интерфейсные шины, в том числе 64- и 32-битовая шины, и выход на системную шину к оперативной памяти (То RAM).

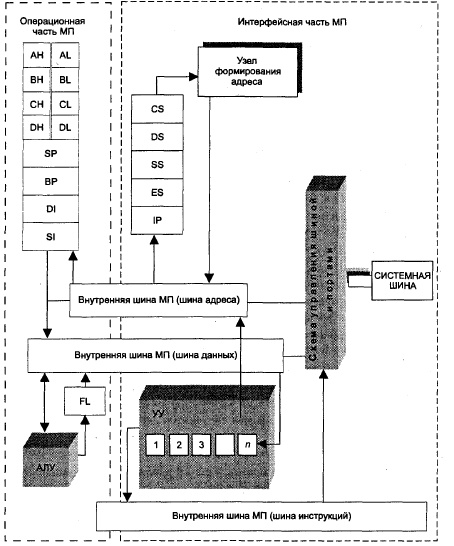

Функционально МП можно разделить на две части:

- операционную, содержащую устройство управления (УУ), арифметико-логическое устройство (АЛУ) и микропроцессорную память (МПП) (за исключением нескольких адресных регистров);

- интерфейсную, содержащую адресные регистры МПП; блок регистров команд — регистры памяти для хранения кодов команд, выполняемых в ближайшие такты; схемы управления шиной и портами.

Обе части МП работают параллельно, причем интерфейсная часть опережает операционную, так что выборка очередной команды из памяти (ее запись в блок регистров команд и предварительный анализ) происходит во время выполнения операционной частью предыдущей команды. Современные микропроцессоры имеют несколько групп регистров в интерфейсной части, работающих с различной степенью опережения, что позволяет выполнять операции в конвейерном режиме. Такая организация МП позволяет существенно повысить его эффективное быстродействие.

1.5. Устройство управления

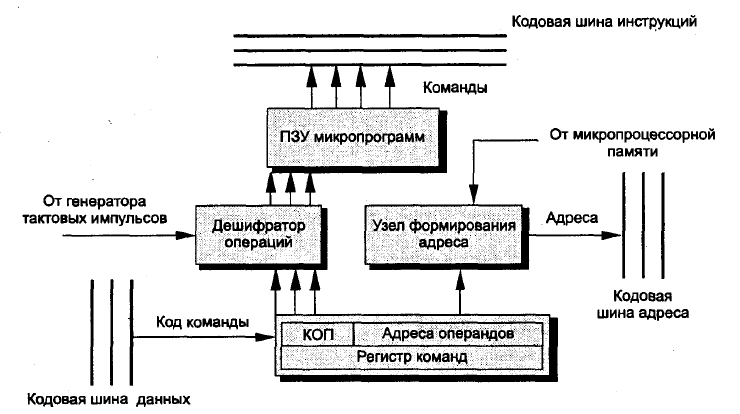

Устройство управления (УУ) является функционально наиболее сложным устройством ПК — оно вырабатывает управляющие сигналы, поступающие по кодовым шинам инструкций (КШИ) во все блоки машины. Упрощенная функциональная схема УУ показана на рис. 5.1. На рисунке представлены:

- регистр команд — запоминающий регистр, в котором хранится код команды — код выполняемой операции (КОП) и адреса операндов, участвующих в операции. Регистр команд расположен в интерфейсной части МП, в блоке регистров команд;

- дешифратор операций — логический блок, выбирающий в соответствии с поступающим из регистра команд кодом операции (КОП) один из множества имеющихся у него выходов;

- постоянное запоминающее устройство (ПЗУ) микропрограмм хранит в своих ячейках управляющие сигналы (импульсы), необходимые для выполнения в блоках ПК процедур обработки информации. Импульс по выбранному дешифратором операций в соответствии с кодом операции проводу считывает из ПЗУ микропрограмм необходимую последовательность управляющих сигналов;

- узел формирования адреса (находится в интерфейсной части МП) — устройство, вычисляющее полный адрес ячейки памяти (регистра) по реквизитам, поступающим из регистра команд и регистров МПП;

- кодовые шины данных, адреса и инструкций — часть внутренней интерфейсной шины микропроцессора.

В общем случае УУ формирует управляющие сигналы для выполнения следующих основных процедур:

- выборка из регистра-счетчика адреса команды МПП адреса ячейки ОЗУ, где хранится очередная команда программы;

- выборка из ячеек ОЗУ кода очередной команды и приема считанной команды в регистр команд;

- расшифровка кода операции и признаков выбранной команды;

- считывание из соответствующих расшифрованному коду операции ячеек ПЗУ микропрограмм управляющих сигналов (импульсов), определяющих во всех блоках машины процедуры выполнения заданной операции, и пересылка управляющих сигналов в эти блоки;

- считывание из регистра команд и регистров МПП отдельных составляющих адресов операндов (чисел), участвующих в вычислениях, и формирование полных адресов операндов;

- выборка операндов (по сформированным адресам) и выполнение заданной операции обработки этих операндов;

- запись результатов операции в память;

- формирование адреса следующей команды программы.

Рис. 1. Укрупненная функциональная схема УУ

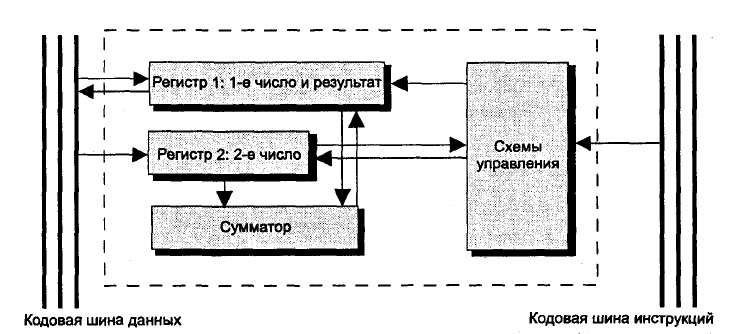

Арифметико-логическое устройство (АЛУ) предназначено для выполнения арифметических и логических операций преобразования информации. Функционально АЛУ состоит обычно из двух регистров, сумматора и схем управления (местного устройства управления).

Сумматор — вычислительная схема, выполняющая процедуру сложения поступающих на ее вход двоичных кодов; сумматор имеет разрядность двойного машинного слова.

Регистры — быстродействующие ячейки памяти различной длины: регистр 1 имеет разрядность двойного слова, а регистр 2 — разрядность слова. При выполнении операций в регистр 1 помещается первое число, участвующее в операции, а по завершении операции — результат; в регистр 2 — второе число, участвующее в операции (по завершению операции информация в нем не изменяется). Регистр 1 может и принимать информацию с кодовых шин данных и выдавать информацию на них; регистр 2 только получает информацию с этих шин.

Схемы управления принимают по кодовым шинам инструкций управляющие сигналы от устройства управления и преобразуют их в сигналы для управления работой регистров и сумматора АЛУ.

АЛУ выполняет арифметические операции «+», «-», «х» и «> только над двоичной информацией с запятой, фиксированной после последнего разряда, то есть только над целыми двоичными числами. Выполнение операций над двоичными числами с плавающей запятой и над двоично-кодированными десятичными числами осуществляется с привлечением математического сопроцессора или по специально составленным программам.

Рассмотрим в качестве примера выполнение команды умножения. Перемножаются числа 1101 и 1011 (числа для простоты взяты 4-битовыми). Множимое находится в регистре 1, имеющем удвоенную по отношению к регистру 2 разрядность; множитель размещается в регистре 2. Операция умножения требует для своеговыполнения нескольких тактов. В каждом такте число из регистра 1 проходит в сумматор (имеющий также удвоенную разрядность) только в том случае, если в младшем разряде регистра 2 находится 1. В данном примере в первом такте число 1101 пройдет в сумматор, и в этом же первом такте число в регистре 1 сдвигается на 1 разряд влево, а число в регистре 2 — на 1 разряд вправо. В конце такта после сдвигов в регистре 1 будет находиться число 11010, а в регистре 2 — число 101. Во втором такте число из регистра 1 пройдет в сумматор, так как младший разряд в регистре 2 равен 1; в конце такта числа в регистрах опять будут сдвинуты влево и вправо, так, что в регистре 1 окажется число 110100, а в регистре 2 — число 10. В третьем такте число из регистра 1 не пройдет в сумматор, так как младший разряд в регистре 2 равен 0; в конце такта числа в регистрах будут сдвинуты влево и вправо, так что в регистре 1 окажется число 1101000, а в регистре 2 — число 1. На четвертом такте число из регистра 1 пройдет в сумматор, поскольку младший разряд в регистре 2 равен 1; в конце такта числа в регистрах будут сдвинуты влево и вправо, так что в регистре 1 окажется число 11010000, а в регистре 2 — число 0. Поскольку множитель в регистре 2 стал равным 0, операция умножения заканчивается. В результате в сумматор последовательно поступят и будут сложены числа: 1101, 11010, 1101000; их сумма 10001111 (143 в десятичной системе) и будет равна произведению чисел 1101 х 1011 (13 х 11 десятичные).

Рис. 2. Функциональная схема АЛУ

1.6. Микропроцессорная память

Микропроцессорная память (МПП) базового МП 8088 включает в себя 14 двухбайтовых запоминающих регистров. У МП 80286 и выше имеются дополнительные регистры, например, у МП типа VLIW есть 256 регистров, из которых 128 — регистры общего назначения. У МП 80386 и выше некоторые регистры, в том числе и регистры общего назначения, — 4-байтовые (у МП Pentium есть и восьмибайтовые регистры). Но в качестве базовой модели, в частности для языка программирования ассемблер и отладчика программ Debug, используется 14-ре-гистровая система МПП. Все регистры можно разделить на 4 группы:

- универсальные регистры: АХ, ВХ, СХ, DX;

- сегментные регистры: CS, DS, SS, ES;

- регистры смещения: IP, SP, BP, SI, DI;

- регистр флагов: FL.

Если регистры 4-байтовые или 8-байтовые, их имена несколько изменяются, например 4-байтовые универсальные регистры АХ, ВХ, СХ, DX именуются соответственно ЕАХ, ЕВХ, ЕСХ, EDX. При этом если используется их двухбайтовая или однобайтовая часть, наименования этих частей регистров соответствуют рассматриваемым ниже.

Регистры АХ, ВХ, СХ и DX являются универсальными (их часто называют регистрами общего назначения — РОН); каждый из них может использоваться для временного хранения любых данных, при этом позволено работать с каждым регистром целиком, а можно отдельно и с каждой его половиной (регистры АН, ВН, СН, DH — старшие (High) байты, а регистры AL, BL, CL, DL — младшие (Low) байты соответствующих 2-байтовых регистров). Но каждый из универсальных регистров может использоваться и как специальный при выполнении некоторых конкретных команд программы. В частности:

- регистр АХ — регистр-аккумулятор, через его порты осуществляется ввод-вывод данных в МП, а при выполнении операций умножения и деления АХ используется для хранения первого числа, участвующего в операции (множимого, делимого), и результата операции (произведения, частного) после ее завершения;

- регистр ВХ часто используется для хранения адреса базы в сегменте данных и начального адреса поля памяти при работе с массивами;

- регистр СХ — регистр-счетчик, используется как счетчик числа повторений при циклических операциях;

- регистр DX используется как расширение регистра-аккумулятора при работе с 32-разрядными числами и при выполнении операций умножения и деления, используется для хранения номера порта при операциях ввода-вывода и т. д.

Регистры сегментной адресации CS, DS, SS, ES используются для хранения начальных адресов полей памяти (сегментов), отведенных в программах для хранения1:

- команд программы (сегмент кода — CS);

- данных (сегмент данных — DS);

- стековой области памяти (сегмент стека — SS);

- дополнительной области памяти данных при межсегментных пересылках (расширенный сегмент — ES), поскольку размер сегмента в реальном режиме работы МП ограничен величиной 64 Кбайт.

Регистры смещений (внутрисегментной адресации) IP, SP, BP, SI, DI предназначены для хранения относительных адресов ячеек памяти внутри сегментов (смещений относительно начала сегментов):

- регистр IP (Instruction Pointer) хранит смещение адреса текущей команды программы;

- регистр SP (Stack Pointer) — смещение вершины стека (текущего адреса стека);

- регистр BP (Base Pointer) — смещение начального адреса поля памяти, непосредственно отведенного под стек;

- регистры SI, DI (Source Index и Destination Index соответственно) предназначены для хранения адресов индекса источника и приемника данных при операциях над строками и им подобных.

Регистр флагов FL содержит условные одноразрядные признаки-маски, или флаги, управляющие прохождением программы в ПК; флаги работают независимо друг от друга, и лишь для удобства они помещены в единый регистр. Всего в регистре содержится 9 флагов: 6 из них статусные, отражают результаты операций, выполненных в компьютере (их значения используются, например, при выполнении команд условной передачи управления — команд ветвления программы), а 3 других — управляющие, непосредственно определяют режим исполнения программы.

- CF (Carry Flag) — флаг переноса. Содержит значение «переносов» (0 или 1) из старшего разряда при арифметических операциях и некоторых операциях сдвига и циклического сдвига;

- PF (Parity Flag) — флаг четности. Проверяет младшие восемь битов результатов операций над данными. Нечетное число единичных битов приводит к установке этого флага в 0, а четное — в 1;

- AF (Auxiliary Carry Flag) — флаг логического переноса в двоично-десятичной арифметике. Вспомогательный флаг переноса устанавливается в 1, если арифметическая операция приводит к переносу или заему четвертого справа бита однобайтового операнда. Этот флаг используется при арифметических операциях над двоично-десятичными кодами и кодами ASCII;

- ZF (Zero Flag) — флаг нуля. Устанавливается в 1, если результат операции равен нулю; если результат не равен нулю, ZF обнуляется;

- SF (Sign Flag) — флаг знака. Устанавливается в соответствии со знаком результата после арифметических операций: положительный результат устанавливает флаг в 0, отрицательный — в 1;

- OF (Overflow Flag) — флаг переполнения. Устанавливается в 1 при арифметическом переполнении: если возник перенос в знаковый разряд при выполнении знаковых арифметических операций, если частное от деления слишком велико и переполняет регистр результата и т. д.

- TF (Trap Flag) — флаг системного прерывания (трассировки). Единичное состояние этого флага переводит процессор в режим пошагового выполнения программы (режим трассировки);

- IF (Interrupt Flag) — флаг прерываний. При нулевом состоянии этого флага прерывания запрещены, при единичном — разрешены;

DF (Direction Flag) — флаг направления. Используется в строковых операциях для задания направления обработки данных. При нулевом состоянии флага команда увеличивает содержимое регистров SI и DI на единицу, обусловливая обработку строки «слева направо»; при единичном — «справа налево»

1.7. Интерфейсная часть МП

Интерфейсная часть МП предназначена для связи и согласования МП с системной шиной ПК, а также для приема, предварительного анализа команд выполняемой программы и формирования полных адресов операндов и команд. Интерфейсная часть включает в свой состав:

- адресные регистры МПП;

- узел формирования адреса;

- блок регистров команд, являющийся буфером команд в МП;

- внутреннюю интерфейсную шину МП;

- схемы управления шиной и портами ввода-вывода.

Некоторые из названных устройств, такие как узел формирования адреса и регистр команды, непосредственно выполняемой МП, функционально входят в состав устройства управления.

Порты ввода-вывода — это пункты системного интерфейса ПК, через которые МП обменивается информацией с другими устройствами. Всего портов у МП может быть 65 536 (равно количеству разных адресов, которые можно представить числом формата «слово»). Каждый порт имеет адрес — номер порта; по существу это адрес ячейки памяти, являющейся частью устройства ввода-вывода, использующего этот порт, а не частью основной памяти компьютера.

Порту устройства соответствуют аппаратура сопряжения и два регистра памяти — для обмена данными и управляющей информацией. Некоторые внешние устройства используют и основную память для хранения больших объемов информации, подлежащей обмену. Многие стандартные устройства (НЖМД, НГМД, клавиатура, принтер, сопроцессор и т. д.) имеют постоянно закрепленные за ними порты ввода-вывода.

Схема управления шиной и портами выполняет следующие функции:

- формирование адреса порта и управляющей информации для него (переключение порта на прием или передачу и т. д.);

- прием управляющей информации от порта, информации о готовности порта и его состоянии;

- организация сквозного канала в системном интерфейсе для передачи данных между портом устройства ввода-вывода и МП.

Схема управления шиной и портами использует для связи с портами кодовые шины инструкций, адреса и данных системной шины: при доступе к порту МП посылает сигнал по кодовой шине инструкций (КШИ), который оповещает все устройства ввода-вывода, что адрес на кодовую шину адреса (КША) является адресом порта, а затем посылает и сам адрес порта. Устройство с совпадающим адресом порта дает ответ о готовности. После чего по кодовой шине данных (КШД) осуществляется обмен данными.

Упрощенная структурная схема микропроцессора показана на рис. 3.

Рис. 3. Упрощенная структурная схема микропроцессора

Глава 2. Архитектура микропроцессора.

Хотя микропроцессор является универсальным средством для цифровой обработки информации, однако отдельные области применения требуют реализации определенных специфических вариантов их структуры и архитектуры. Поэтому по функциональному признаку выделяются два класса: микропроцессоры общего назначения и специализированные микропроцессоры (рис. 1.3).

Рис. 4. Классификация современных микропроцессоров по функциональному признаку

Среди специализированных микропроцессоров наиболее широкое распространение получили микроконтроллеры, предназначенные для выполнения функций управления различными объектами, и цифровые процессоры сигналов (DSP - Digital Signal Processor), которые ориентированы на реализацию процедур, обеспечивающих необходимое преобразование аналоговых сигналов, представленных в цифровой форме (в виде последовательности числовых значений).

Микропроцессоры общего назначения предназначены для решения широкого круга задач обработки разнообразной информации. Их основной областью использования являются персональные компьютеры, рабочие станции, серверы и другие цифровые системы массового применения. К этому классу относятся CISC-процессоры Pentium компании «Intel», K7 - компании «Advanced MicroDevices» (AMD), 680x0 - компании «Motorola», RISC-процессоры PowerPC, выпускаемые компаниями «Motorola» и IBM, SPARC - компании «Sun Microsystems» и ряд других изделий различных производителей.

Расширение области применения таких микропроцессоров достигается главным образом путем роста производительности, благодаря чему увеличивается круг задач, который можно решать с их использованием. Поэтому повышение производительности является магистральным направлением развития этого класса микропроцессоров. Обычно это 32-разрядные микропроцессоры (некоторые микропроцессоры этого класса имеют 64-разрядную или 128-разрядную структуру), которые изготавливаются по самой современной промышленной технологии, обеспечивающей максимальную частоту функционирования.

Ряд наиболее популярных микропроцессоров этого класса (Pentium, AMD K7 и некоторые другие) следует отнести к CISC-процессорам, так как они выполняют большой набор разноформатных команд с использованием многочисленных способов адресации. Однако в их внутренней структуре содержится RISC-процессор, который выполняет поступившие команды после их преобразования в последовательность простых RISC-операций. Ряд других микропроцессоров этого класса непосредственно реализует RISC-архитектуру. Поэтому можно считать, что использование RISC-архитектуры характерно 1ля большинства этих микропроцессоров. Однако в ряде последних разработок (Itanium, DA8500) некоторых ведущих производителей успешно применяются принципы VLIW-apхитектуры, которая может составить конкуренцию RISC-архитектуре в соревновании за достижение наивысшей производительности.

Практически все современные микропроцессоры этого класса используют Гарвардскую внутреннюю архитектуру, где разделение потоков команд и данных реализуется с помощью отдельных блоков кэш-памяти. В большинстве случаев они имеют суперскалярную структуру с несколькими исполнительными конвейерами (до 10 в современных моделях), которые содержат до 20 ступеней.

Благодаря своей универсальности микропроцессоры общего назначения используются также в специализированных системах, где требуется высокая производительность. На их основе реализуются одноплатные компьютеры и промышленные компьютеры, которые применяются в системах управления различными объектами. Одноплатные (встраиваемые) компьютеры содержат на плате необходимые дополнительные микросхемы, обеспечивающие их специализированное применение, и предназначены доя встраивания в аппаратуру различного назначения. Промышленные компьютеры размещаются в корпусах специальной конструкции, обеспечивающих их надежную работу в жестких производственных условиях. Обычно такие компьютеры работают без стандартных периферийных устройств (монитор, клавиатура, «мышь») или используют специальные варианты этих устройств, модифицированные с учетом специфических условий применения.

Микроконтроллеры являются специализированными микропроцессорами, которые ориентированы на реализацию устройств управления, встраиваемых в разнообразную аппаратуру. Ввиду огромного количества объектов, управление которыми обеспечивается с помощью микроконтроллеров, годовой объем их выпуска превышает 2 миллиарда экземпляров, на порядок превосходя объем выпуска микропроцессоров общего применения. Весьма широкой является также номенклатура выпускаемых микроконтроллеров, которая содержит несколько тысяч типов.

Характерной особенностью структуры микроконтроллеров является размещение на :дном кристалле с центральным процессором внутренней памяти и большого набора периферийных устройств. В состав периферийных устройств обычно входят несколько 3-разрядных параллельных портов ввода-вывода данных (от 1 до 8), один или два последовательных порта, таймерный блок, аналого-цифровой преобразователь. Кроме того, различные типы микроконтроллеров содержат дополнительные специализированные устройства - блок формирования сигналов с широтно-импульсной модуляцией, контроллер жидкокристаллического дисплея и ряд других. Благодаря использованию внутренней памяти и периферийных устройств реализуемые на базе микроконтроллеров системы управления содержат минимальное количество дополнительных компонентов.

В связи с широким диапазоном решаемых задач управления требования, предъявляемые к производительности процессора, объему внутренней памяти команд и данных, набору необходимых периферийных устройств, оказываются весьма разнообразными. Для удовлетворения запросов потребителей выпускается большая номенклатура микроконтроллеров, которые принято подразделять на 8-, 16- и 32-разрядные.

• 8-разрядные микроконтроллеры представляют наиболее многочисленную группу этого класса микропроцессоров, которые имеют относительно низкую производительность, которая, однако, вполне достаточна для решения широкого круга задач управления различными объектами. Это простые и дешевые микроконтроллеры, ориентированные на использование в относительно несложных устройствах массового выпуска. Основными областями их применения являются бытовая и измерительная техника, промышленная автоматика, автомобильная электроника, теле-, видео- и аудиоаппаратура, средства связи.

Для этих микроконтроллеров характерна реализация Гарвардской архитектуры, где используется отдельная память для хранения программ и данных. Для хранения программ в различных типах микроконтроллеров применяется либо масочно-программируемое ПЗУ (ROM), либо однократно-программируемое ПЗУ (PROM), либо электрически репрограммируемое ПЗУ (EPROM, EEPROM или Flash). Внутренняя память программ обычно имеет объем от нескольких единиц до десятков Кбайт. Для хранения данных используется регистровый блок, организованный в виде нескольких регистровых банков, или внутреннее ОЗУ. Объем внутренней памяти данных составляет от нескольких десятков байт до нескольких Кбайт. Ряд микроконтроллеров этой группы позволяет в случае необходимости дополнительно подключать внешнюю память команд и данных, объемом до 64-256 Кбайт.

Микроконтроллеры этой группы обычно выполняют относительно небольшой набор команд (50-100), использующих наиболее простые способы адресации. В ряде последних моделей этих микроконтроллеров реализованы принципы RISC-архитектуры, что позволяет существенно повысить их производительность. В результате такие микроконтроллеры обеспечивают выполнение большинства команд за один такт машинного времени.

• 16-разрядные микроконтроллеры во многих случаях являются усовершенствованной

модификацией своих 8-разрядных прототипов. Они характеризуются не только увеличенной разрядностью обрабатываемых данных, но и расширенной системой команд и способов адресации, увеличенным набором регистров и объемом адресуемой памяти, а также рядом других дополнительных возможностей, использование которых позволяет повысить производительность и обеспечить новые области применения. Обычно эти микроконтроллеры позволяют расширить объем памяти программ и данных до нескольких Мбайт путем подключения внешних микросхем памяти. Во многих случаях реализуется их программная совместимость с более младшими 8-разрядными моделями. Основная сфера применения таких микроконтроллеров - сложная промышленная автоматика, телекоммуникационная аппаратура, медицинская и измерительная техника.

• 32-разрядные микроконтроллеры содержат высокопроизводительный процессор, соответствующий по своим возможностям младшим моделям микропроцессоров общего назначения. В ряде случаев процессор, используемый в этих микроконтроллерах, аналогичен CISC- или RISC-процессорам, которые выпускаются или выпускались ранее в качестве микропроцессоров общего назначения. Например, в 32-разрядных микроконтроллерах компании Intel используется процессор i386, в микроконтроллерах компании Motorola широко применяется процессор 680x0, в ряде других микроконтроллеров в качестве процессорного ядра служат RISC-процессоры типа PowerPC. На базе данных процессоров были реализованы различные модели персональных компьютеров. Введение этих процессоров в состав микроконтроллеров позволяет использовать в соответствующих системах управления огромный объем прикладного и системного программного обеспечения, созданный ранее для соответствующих персональных компьютеров.

Кроме 32-разрядного процессора на кристалле микроконтроллера размещается внутренняя память команд емкостью до десятков Кбайт, память данных емкостью до нескольких Кбайт, а также сложно-функциональные периферийные устройства -таймерный процессор, коммуникационный процессор, модуль последовательного обмена и ряд других. Микроконтроллеры работают е внешней памятью объемом до 16 Мбайт и выше. Они находят широкое применение в системах управления сложными объектами промышленной автоматики (двигатели, робототехнические устройства, средства комплексной автоматизации производства), в контрольно-измерительной аппаратуре и телекоммуникационном оборудовании.

Во внутренней структуре этих микроконтроллеров реализуется Принстонская или Гарвардская архитектура. Входящие в их состав процессоры могут иметь CISC- или RISC-архитектуру, а некоторые из них содержат несколько исполнительных конвейеров, образующих суперскалярную структуру.

Цифровые процессоры сигналов (ЦПС) представляют класс специализированных микропроцессоров, ориентированных на цифровую обработку поступающих аналоговых сигналов. Специфической особенностью алгоритмов обработки аналоговых сигналов определяется необходимость последовательного выполнения ряда команд умножения-сложения с накоплением промежуточного результата в регистре-аккумуляторе. Поэтому ap-i/тектура ЦПС ориентирована на реализацию быстрого выполнения операций такого рода. Набор команд этих процессоров содержит специальные команды MAC (Multiplication Aith Accumlation), реализующие эти операции.

Значение поступившего сигнала может быть представлено в виде числа с фиксированной или с «плавающей» точкой. В соответствии с этим ЦПС делятся на процессоры, обрабатывающие числа с фиксированной или плавающей точкой. Более простые и дешевые ЦПС с фиксированной точкой обычно обрабатывают 16-разрядные операнды, представленные а виде правильной дроби. Однако ограниченная разрядность в ряде случаев не позволяет обеспечить необходимую точность преобразования. Поэтому в ЦПС с фиксированной точкой, выпускаемых компанией «Motorola», принято 24-разрядное представление операндов. Наиболее высокая точность обработки обеспечивается в случае представления даныхв формате с «плавающей» точкой. В ЦПС, обрабатывающих данные с «плавающей» точкой,обычно используется 32-разрядный формат их представления.

Для повышения производительности при выполнении специфических операций обработки сигналов в большинстве ЦПС реализуется Гарвардская архитектура с использованием нескольких шин для передачи адресов, команд и данных. В ряде ЦПС нашли применение также некоторые черты VLIW-архитектуры: совмещение в одной команде нескольку операций, обеспечивающих обработку имеющихся данных и одновременную загрузку = исполнительный конвейер новых данных для последующей обработки.

Архитектурой процессора называется комплекс его аппаратных и программных средств, предоставляемых пользователю. В это общее понятие входит набор программно-доступных регистров и исполнительных (операционных) устройств, система основных команд и способов адресации, объем и структура адресуемой памяти, виды и способы обработки прерываний.

Например, все модификации процессоров Pentium, Celeron, i486 и i386 имеют архитектуру IA-32 (Intel Architecture - 32 bit), которая характеризуется стандартным набором регистров, предоставляемых пользователю, общей системой основных команд и способов организации и адресации памяти, одинаковой реализацией защиты памяти и обслуживания прерываний.

При описании архитектуры и функционирования процессора обычно используется его представление в виде совокупности программно-доступных регистров, образующих регистровую или программную модель. В этих регистрах содержатся обрабатываемые данные (операнды) и управляющая информация. Соответственно, в регистровую модель входит группа регистров общего назначения, служащих для хранения операндов, и группа служебных регистров, обеспечивающих управление выполнением программы и режимом работы процессора, организацию обращения к памяти (защита памяти, сегментная и страничная организация и др.).

Регистры общего назначения образуют РЗУ - внутреннюю регистровую память процессора. Состав и количество служебных регистров определяется архитектурой микропроцессора. Обычно в их состав входят:

• программный счетчик PC (или CS + IP в архитектуре микропроцессоров Intel);

• регистр состояния SR (или EFLAGS);

• регистры управления режимом работы процессора CR (Control Register);

• регистры, реализующие сегментную и страничную организацию памяти;

• регистры, обеспечивающие отладку программ и тестирование процессора.

Кроме того, различные модели микропроцессоров содержат ряд других специализированных регистров.

Функционирование процессора представляется в виде реализации регистровых пересылок - процедур изменения состояния этих регистров путем чтения-записи их содержимого. В результате таких пересылок обеспечивается адресация и выбор команд и операндов, хранение и пересылка результатов, изменение последовательности команд и режимов функционирования процессора в соответствии с поступлением нового содержимого в служебные регистры, а также все другие процедуры, реализующие процесс обработки информации согласно заданным условиям.

В ряде процессоров выделяются регистры, которые используются при выполнении прикладных программ и доступны каждому пользователю, и регистры, которые управляют режимом работы всей системы и доступны только для привилегированных программ, входящих в состав операционной системы (супервизора). Соответственно, такие процессоры представляются в виде регистровой модели пользователя, в которую входят регистры, используемые при выполнении прикладных программ, или регистровой модели супервизора, которая содержит весь набор программно-доступных регистров процессора, используемых операционной системой.

Структура микропроцессора определяет состав и взаимодействие основных устройств и блоков, размещенных на его кристалле. В эту структуру входят:

• центральный процессор (процессорное ядро), состоящее из устройства управления (УУ), одного или нескольких операционных устройств (ОУ);

• внутренняя память (РЗУ, кэш-память, блоки оперативной и постоянной памяти);

• интерфейсный блок, обеспечивающий выход на системную шину и обмен данными с внешними устройствами через параллельные или последовательные порты ввода/вывода;

• периферийные устройства (таймерные модули, аналого-цифровые преобразователи, специализированные контроллеры);

• различные вспомогательные схемы (генератор тактовых импульсов, схемы для выполнения отладки и тестирования, сторожевой таймер и ряд других).

Состав устройств и блоков, входящих в структуру микропроцессора, и реализуемые механизмы их взаимодействия определяются функциональным назначением и областью применения микропроцессора.

Архитектура и структура микропроцессора тесно взаимосвязаны. Реализация тех или иных архитектурных особенностей требует введения в структуру микропроцессора необходимых аппаратных средств (устройств и блоков) и обеспечения соответствующих механизмов их совместного функционирования.

В современных микропроцессорах реализуются следующие варианты архитектур.

CISC(Complex Instruction Set Computer)-apxumeкmypa реализована во многих типах микропроцессоров, выполняющих большой набор разноформатных команд с использованием многочисленных способов адресации. Эта классическая архитектура процессоров, которая начала свое развитие в 1940-х годах с появлением первых компьютеров. Типичным примером CISC-процессоров являются микропроцессоры семейства Pentium. Они выполняют более 200 команд разной степени сложности, которые имеют размер от 1 до 15 байт и обеспечивают более 10 различных способов адресации. Такое большое многообразие выполняемых команд и способов адресации позволяет программисту реализовать наиболее эффективные алгоритмы решения различных задач. Однако при этом существенно усложняется структура микропроцессора, особенно его устройства управления, что приводит к увеличению размеров и стоимости кристалла, снижению производительности. В тоже время многие команды и способы адресации используются достаточно редко. Поэтому, начиная с 1980-х годов, интенсивное развитие получила архитектура процессоров с сокращенным набором команд (RISC-процессоры).

RISC (Reduced Instruction Set Computer)-архитектура отличается использованием ограниченного набора команд фиксированного формата. Современные RISC-процессоры обычно реализуют около 100 команд, имеющих фиксированный формат длиной 4 байта. Также значительно сокращается число используемых способов адресации. Обычно в RISC-процессорах все команды обработки данных выполняются только с регистровой или непосредственной адресацией. При этом для сокращения количества обращений к памяти RISC-процессоры имеют увеличенный объем внутреннего РЗУ - от 32 до нескольких сотен регистров, тогда как в CISC-процессорах число регистров общего назначения обычно составляет 8-16.

Обращение к памяти в RISC-процессорах используется только в операциях загрузки данных в РЗУ или пересылки результатов из РЗУ в память. При этом используется небольшое число наиболее простых способов адресации: косвенно-регистровая, индексная и некоторые другие. В результате существенно упрощается структура микропроцессора, сокращаются его размеры и стоимость, значительно повышается производительность.

Указанные достоинства RISC-архитектуры привели к тому, что во многих современных CISC-процессорах используется RISC-ядро, выполняющее обработку данных. При этом поступающие сложные и разноформатные команды предварительно преобразуются в последовательность простых RISC-операций, быстро выполняемых этим процессорным ядром. Таким образом, работают, например, последние модели микропроцессоров Pentium и К7, которые по внешним показателям относятся к CISC-процессорам. Использование RISC-архитектуры является характерной чертой многих современных микропроцессоров.

VLIW (Very Large Instruction Word)-арxитeктyра появилась относительно недавно — в 1990-х годах. Ее особенностью является использование очень длинных команд (до 128 бит и более), отдельные поля которых содержат коды, обеспечивающие выполнение различных операций. Таким образом, одна команда вызывает выполнение сразу нескольких операций параллельно в различных операционных устройствах, входящих в структуру микропроцессора. При трансляции программ, написанных на языке высокого уровня, соответствующий компилятор производит формирование «длинных» VLIW-команд, каждая из которых обеспечивает реализацию процессором целой процедуры или группы операций. Данная архитектура реализована в некоторых типах современных микропроцессоров (РА8500 компании «Hewlett-Packard», Itanium -совместная разработка «Intel» и « Hewlett-Packard», некоторые типы DSP - цифровых процессоров сигналов) и является весьма перспективной для создания нового поколения сверхвысокопроизводительных процессоров.

Кроме набора выполняемых команд и способов адресации важной архитектурной особенностью микропроцессоров является используемый вариант реализации памяти и организация выборки команд и данных. По этим признакам различаются процессоры с Принстонской и Гарвардской архитектурой. Эти архитектурные варианты были предложены в конце 1940-х годов специалистами соответственно Принстонского и Гарвардского университетов США для разрабатываемых ими моделей компьютеров.

Принстонская архитектура, которая часто называется архитектурой Фон-Неймана, характеризуется использованием общей оперативной памяти для хранения программ, данных, а также для организации стека. Для обращения к этой памяти используется общая системная шина, по которой в процессор поступают и команды, и данные. Эта архитектура имеет ряд важных достоинств. Наличие общей памяти позволяет оперативно перераспределять ее объем для хранения отдельных массивов команд, данных и реализации стека в зависимости от решаемых задач. Таким образом, обеспечивается возможность более эффективного использования имеющегося объема оперативной памяти в каждом конкретном случае применения микропроцессора. Использование общей шины для передачи команд и данных значительно упрощает отладку, тестирование и текущий контроль функционирования системы, повышает ее надежность. Поэтому Принстонская архитектура в течение долгого времени доминировала в вычислительной технике.

Однако ей присущи и существенные недостатки. Основным из них является необходимость последовательной выборки команд и обрабатываемых данных по общей системной шине. При этом общая шина становится «узким местом» (bottleneck - «бутылочное горло»), которое ограничивает производительность цифровой системы. Постоянно возрастающие требования к производительности микропроцессорных систем вызвали в последние годы все более широкое применение Гарвардской архитектуры при создании многих типов современных микропроцессоров.

Гарвардская архитектура характеризуется физическим разделением памяти команд (программ) и памяти данных. В ее оригинальном варианте использовался также отдельный стек для хранения содержимого программного счетчика, который обеспечивал возможности выполнения вложенных подпрограмм. Каждая память соединяется с процессором отдельной шиной, что позволяет одновременно с чтением-записью данных при выполнении текущей команды производить выборку и декодирование следующей команды. Благодаря такому разделению потоков команд и данных и совмещению операций их выборки реализуется более высокая производительность, чем при использовании Принстонской архитектуры.

Недостатки Гарвардской архитектуры связаны с необходимостью проведения большего числа шин, а также с фиксированным объемом памяти, выделенной для команд и данных, назначение которой не может оперативно перераспределяться в соответствии с требованиями решаемой задачи. Поэтому приходится использовать память большего объема, коэффициент использования которой при решении разнообразных задач оказывается более низким, чем в системах с Принстонской архитектурой. Однако развитие микроэлектронной технологии позволило в значительной степени преодолеть указанные недостатки, поэтому Гарвардская архитектура широко применяется во внутренней структуре современных высокопроизводительных микропроцессоров, где используется отдельная кэш-память для хранения команд и данных. В то же время во внешней структуре большинства микропроцессорных систем реализуются принципы Принстонской архитектуры.

Гарвардская архитектура получила также широкое применение в микроконтроллерах - специализированных микропроцессорах для управления различными объектами, рабочая программа которых обычно хранится в отдельном ПЗУ.

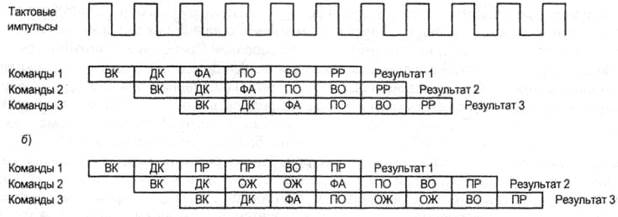

Во внутренней структуре современных высокопроизводительных микропроцессоров реализуется конвейерный принцип выполнения команд. При этом процесс выполнения команды разбивается на ряд этапов. На рис. 1.1, а приведен пример разбиения команды на шесть этапов ее выполнения:

1) выборка очередной команды (ВК);

2) декодирование выбранной команды (ДК);

3) формирование адреса операнда (ФА);

4) прием операнда из памяти (ПО);

5) выполнение операции (ВО);

6) размещение результата в памяти (РР).

Реализация каждого этапа занимает один такт машинного времени и производится устройствами и блоками процессора, образующими ступени исполнительного конвейера, на каждой из которых выполняется соответствующая микрооперация. При последовательной загрузке в конвейер выбираемых команд каждая его ступень реализует определенный этап выполнения очередной команды. Таким образом, в конвейере одновременно находятся несколько команд, находящихся на разных этапах выполнения. В идеальном варианте при полной загрузке конвейера на его выход в каждом такте будет поступать результат выполнения очередной команды (рис. 1.1, а). В этом случае производительность процессора (операций/с) будет равна его тактовой частоте (тактов/с).

Однако такая эффективная работа конвейера обеспечивается только при его равномерной загрузке однотипными командами. Реально отдельные ступени конвейера могут оказаться незагруженными, находясь в состоянии ожидания или простоя. Ожиданием называется состояние исполнительной ступени, когда она не может выполнить требуемую микрооперацию, так как еще не получен необходимый операнд, являющийся результатом выполнения предыдущей команды. Простоем называется состояние ступени, когда она вынуждена пропустить очередной такт, так как поступившая команда не требует выполнения соответствующего этапа. Например, при выполнении безадресных команд не требуется производить формирование адреса и прием операнда (простой на ступенях ФА и ПО конвейера).

Рис. 5. Реализация конвейерного исполнения команд при идеальной (а) и реальной (б) загрузке 6-ступенчатого конвейера

На рис. 5, б показан пример работы 6-ступенчатого конвейера при выполнении фрагмента реальной программы, когда отдельные ступени оказываются в состоянии ожидания (ОЖ) или простоя (ПР). Команда INC R2, которая увеличивает на 1 содержимое регистра R2, не требует выборки операндов из памяти и размещения в ней результата. Поэтому при ее выполнении реализуется состояние простоя (ПР) на ступенях конвейера, выполняющих микрооперации ФА, ПО, PP. Команда MOV (R2), R3 производит пересылку содержимого ячейки памяти, адресуемой содержимым регистра R2, в регистр R3. При ее выполнении реализуются состояния ожидания (ОЖ), пока в регистре R2 не будет получен результат предыдущей операции. Такты ожидания (ОЖ) вводятся также при выполнении команды сложения ADD R3, (R4) до получения необходимого значения операнда в регистре R3. В результате введения состояний ожиданий и простоя реальная производительность процессора при выполнении данного фрагмента программы составит 5/3 команд/такт, то есть будет в 1,7 раз меньше, чем в идеальном случае (рис. 5, б).

В современных высокопроизводительных микропроцессорах процедура выполнения команд может разбиваться на еще более мелкие этапы, чтобы успеть выполнить соответствующие микрооперации на каждой ступени за один такт, длительность которого при тактовой частоте более 1 ГГц составляет менее наносекунды. Поэтому в таких процессорах число ступеней конвейера достигает 10 и более. Например, в микропроцессорах Pentium 4 используется 20-ступенчатый конвейер.

Эффективность использования конвейера определяется типом поступающих команд. При поступлении однородных команд обеспечивается сокращение числа состояний простоя и ожидания в процессе их выполнения, в результате чего повышается производительность процессора. При использовании в программе разноформатных команд, содержащих различное количество байтов, число состояний простоя и ожидания, которые приходится вводить в процессе выполнения команд, значительно увеличивается. Поэтому принятый во многих RISC-процессорах стандартный 4-байтный формат команд обеспечивает существенное сокращение числа ожиданий и простоев конвейера, что позволяет значительно повысить производительность.

Другой причиной снижения эффективности конвейера являются команды условного ветвления. Если выполняется условие ветвления, то приходится производить перезагрузку конвейера командами из другой ветви программы, что требует выполнения дополнительных рабочих тактов и вызывает значительное снижение производительности. Поэтому одним из основных условий эффективной работы конвейера является сокращение числа его перезагрузок при выполнении условных переходов. Эта цель достигается с помощью реализации различных механизмов предсказания направления ветвления, которые обеспечиваются с помощью специальных устройств - блоков предсказания ветвления, вводимых в структуру процессора.

В современных микропроцессорах используются разнообразные способы предсказания ветвлений. Наиболее простой способ состоит в том, что процессор фиксирует результат выполнения предыдущих команд ветвления по данному адресу и считает, что следующая команда с обращением по этому адресу даст аналогичный результат. Данный способ предсказания предполагает более высокую вероятность повторного обращения к определенной команде, задаваемой данным условием ветвления. Для реализации этого способа предсказания ветвления используется специальная память ВТВ (Branch Target Buffer), где хранятся адреса ранее выполненных условных переходов. При поступлении аналогичной команды ветвления предсказывается переход к ветви, которая была выбрана в предыдущем случае, и производится загрузка в конвейер команд из соответствующей ветви. При правильном предсказании не требуется перезагрузка конвейера и эффективность его использования не снижается. Эффективность такого способа предсказания зависит от емкости ВТВ и оказывается достаточно высокой: вероятность правильного предсказания составляет 80% и более. Повышение точности предсказания достигается при использовании более сложных способов, когда хранится и анализируется предыстория переходов - результаты нескольких предыдущих команд ветвления по данному адресу. В этом случае возможно определение чаще всего реализуемого направления ветвления, а также выявление чередующихся переходов. Реализация таких алгоритмов требует использования более сложных блоков предсказания, но при этом вероятность правильного предсказания повышается до 90-95%.

Возможность повышения производительности процессора достигается также при введении в структуру процессора нескольких параллельно включенных операционных устройств, обеспечивающих одновременное выполнение нескольких операций. Такая структура процессора называется суперскалярной. В этих процессорах реализуется параллельная работа нескольких исполнительных конвейеров, в каждый из которых поступает для выполнения одна из выбранных и декодированных команд. В идеальном случае число одновременно выполняемых команд равно числу операционных устройств, включенных в исполнительные конвейеры. Однако при выполнении реальных программ трудно обеспечить полную загрузку всех исполнительных конвейеров, поэтому на практике эффективность использования суперскалярной структуры оказывается несколько ниже. Современные суперскалярные процессоры содержат до 4 до 10 различных операционных устройств, параллельная работа которых обеспечивает выполнение за один такт в среднем от 2 до 6 команд.

ЗАКЛЮЧЕНИЕ

ЭВМ получили широкое распространение, начиная с 50-х годов. Прежде это были очень большие и дорогие устройства, используемые лишь в государственных учреждениях и крупных фирмах. Размеры и форма цифровых ЭВМ неузнаваемо изменились в результате разработки новых устройств, называемых микропроцессорами.

В данной работе объектом изучения послужили микропроцессоры ПК. Были раскрыты основные понятия, используемые в выбранной теме; дана классификация микропроцессоров и краткая характеристика их элементов; рассмотрена структура и основные характеристики микропроцессоров ПК. Будущее микропроцессорной техники связано сегодня с двумя новыми направлениями — нанотехнологиями и квантовыми вычислительными системами. Эти пока еще главным образом теоретические исследования касаются использования в качестве компонентов логических схем молекул и даже субатомных частиц: основой для вычислений должны служить не электрические цепи, как сейчас, а положение отдельных атомов или направление вращения электронов. Если "микроскопические" компьютеры будут созданы, то они обойдут современные машины по многим параметрам.

СПИСОК ИСПОЛЬЗОВАННОЙ ЛИТЕРАТУРЫ

https://studfiles.net/ — файловый архив студентов.

http://www.internet-law.ru — сайт юридической фирмы «Интернет-право». Использовался для поиска информации о ГОСТе.

http://pue8.ru/ — всё об электротехнике.

http://mirznanii.com/ — информация о разных науках.

http://dfe.petrsu.ru — кафедра информационно-измерительных систем и физической электроники.

http://www.yaklass.ru/ — образовательный проект Сколково.

https://poznayka.org/ — сайт знаний.

https://helpiks.org/ — интернет-помощник.

- Социальное обеспечение: структура и формы (Структура и формы социального обеспечения)

- ИСТОРИЯ СОЗДАНИЯ ОПЕРАЦИОННОЙ СИСТЕМЫ

- Ситуационный подход.

- Прямые налоги и их место в налоговой системе России (Теоретические аспекты прямого налогообложения)

- Облачные сервисы (Обзор сервисов, реализованных на основе облачных технологий)

- Гарантии прав и свобод человека и гражданина .

- Человеческий фактор в управлении организацией ( Профессиональное управление)

- Налоговая система России и проблемы еe совершенствования

- Контроль за оперативно-розыскной деятельностью (Сущность осуществления контроля за оперативно-розыскной деятельностью )

- Законность и правопорядок (Понятие правопорядка)

- Бренд как конкурентное преимущество компании (Стратегия бренда)

- Определение, основные задачи, функции бухгалтерского учета (Сущность бухгалтерского учета )