Процессор персонального компьютера. Назначение, функции, классификация процессора. (ПРИНЦИП РАБОТЫ ПРОЦЕССОРА)

Содержание:

ВВЕДЕНИЕ

Сейчас принято говорить, что центральный процессор - это мозг компьютера. На самом деле, процессор - это крошечный чип, подключенный непосредственно к материнской плате, с большим вентилятором (кулером), подключенным непосредственно к нему. Без вентилятора процессор сгорел бы очень быстро.

Сегодня на рынке существует два основных бренда процессоров: Intel и AMD. Есть также два разных процессора: «сокет» и разъем. Сокет подключен непосредственно к материнской плате, также он имеет свой собственный вентилятор, в то время как разъем имеет оболочку, которая удерживается на процессоре, и вентилятор, подключенный к этой оболочке. Невозможно выделить лучший из этих двух типов, но «сокет» становится все популярнее, и таким образом становится легче охлаждать процессор, что является главным фактором производительности компьютера.

Скорость процессора измеряется в мегагерцах (МГц), более 1000 МГц называется гигагерц (ГГц). Одно из основных заблуждений о процессоре заключается в том, что чем больше число (мегагерц/гигагерц), тем быстрее процессор.

Вопросы, касающиеся архитектуры процессоров рассматривались такими учеными как Х. Крейгон, Д. Паттерсон, и другими. В нашей стране данная проблематика получила свое развитие в трудах таких ученых как Задков В. Н., Кирсанов Э. Ю. и других.

Целью данной курсовой работы является изучение архитектуры, функционирования и основных характеристик процессора.

Для достижения этой цели необходимо решить следующие задачи:

1. Изучите архитектуру процессора

2. Исследуйте функционирование процессора

3. Провести сравнительный анализ основных характеристик процессоров.

Структурно работа состоит из введения, заключения, трех глав и списка использованных источников.

1 ПРИНЦИП РАБОТЫ ПРОЦЕССОРА

Центральный процессор (ЦПУ), или CPU, или процессор ПК - это специальный чип, который выполняет все основные вычислительные операции и выполняет обработку информации. Процессор ПК выполняет программный код-последовательность команд (инструкций), каждая из которых кодируется и помещается в память [6].

В общем случае каждая команда содержит операционную и операндную части. Первый содержит информацию о действиях, которые должен выполнить процессор, а второй указывает процессору операнды - на что процессор должен «работать». Часть операнда описывает до двух операндов инструкции. Это могут быть значения операндов, явные или неявные ссылки на регистры процессора, в которых хранятся операнды, адрес ячейки памяти, регистры процессора и т. д. длина инструкции выражается в байтах.

Логический адрес выполняемой команды (инструкции) хранится в регистре InstructionPointer (указатель инструкции) - счетчике команд. После выполнения значение счетчика увеличивается на длину инструкции, указывая на начало следующей инструкции [9].

Существует два типа инструкций:

- линейный. Выполняются в соответствии с их размещением в памяти в порядке возрастания;

- передача контроля. К ним относятся операторы перехода и вызовы процедур, содержащие адрес следующего исполняемого оператора.

Хотя последовательность выполнения команд четко прописана в коде команды, она может быть нарушена исключениями и прерываниями. Исключения - это особые ситуации, возникающие при выполнении инструкций (управляемых ОС) [12]. Аппаратные прерывания представляют собой процедуру вызова электрических сигналов в специальных выводах на процессоре. Источниками аппаратных прерываний являются, например, контроллеры устройств, системы управления питанием. Кроме того, последовательность команд может быть изменена сигналом перезапуска процессора [12].

При выполнении инструкции процессор извлекает два двоичных числа из указанных в ней мест (регистр, Память, константа) и записывает результат действия над ними на место одного из них. Процессор выполняет арифметические функции (сложение, вычитание, умножение, деление) над целочисленными данными (знаковыми и беззнаковыми, двоичными и двоично-десятичными).

Работа над числами с плавающей запятой (в виде мантиссы и порядка) поручается математическому сопроцессору. Это набор 80-битных регистров и арифметическое устройство, которое помимо четырех арифметических операций вычисляет значение квадратного корня, логарифмы, степени чисел и тригонометрические функции [9].

Архитектура процессора ПК определяется набором команд, регистрами и структурой данных, а микроархитектура является схемотехнической реализацией его архитектуры. Новые микроархитектуры были созданы для производства высокопроизводительных процессоров, таких как IntelNetBurst в процессорах Pentium, или P6 в старых процессорах.

Процессорные исполнительные устройства (для обработки целых чисел и чисел с плавающей запятой) должны непрерывно получать необходимые команды. В микроархитектуре Intel NetBurst применено несколько новинок, обеспечивающих постоянную нагрузку исполнительных блоков. Среди них-системная шина с частотой 400 МГц, кэш L2 с улучшенной передачей данных (AdvancedTransferCache), кэш L1 с отслеживанием выполнения и уменьшенной задержкой для данных, улучшенное динамическое выполнение [7].

Центральный процессор - это центральное устройство компьютера, которое выполняет операции обработки данных и управляет периферийными устройствами компьютера. В компьютерах четвертого поколения и старше функции центрального процессора выполняет микропроцессор на основе СБИС, содержащий несколько миллионов элементов, конструктивно созданных на полупроводниковом кристалле с использованием сложной микроэлектронной технологии [21].

Основные характеристики процессора включают в себя:

- скорость (вычислительная мощность) - среднее число операций процессора в секунду;

- тактовая частота в Мгц. Тактовая частота равна числу циклов в секунду.

Такт - это временной интервал между началом текущего импульса ГТЧ и началом следующего. Типичные тактовые частоты микропроцессоров: 40 МГц, 66 МГц, 100 МГц, 130 МГц, 166 МГц, 200 МГц,333 МГц, 400 МГц, 600 МГц, 800 МГц, 1000 МГц и др. [8]. Тактовая частота до 3 ГГц отражает уровень промышленной технологии, на которой был изготовлен этот процессор. Он также характеризует компьютер, поэтому название модели микропроцессора может быть достаточно полным представлением о том, к какому классу принадлежит компьютер [3]. Поэтому компьютерам часто дают названия микропроцессоров, которые их составляют. Ниже приведены названия самых популярных процессоров, выпущенных компанией Intel, и годы их создания: 8080 (1974), 80286 (1982), 80386DX (1985), 80486DX (1989), 80586 или Pentium (1993), Pentium Pro (1995), Pentium II (1997), Pentium III (1999), Pentium IV (2001). Как видим, увеличение частоты является одной из основных тенденций развития микропроцессоров. На рынке массовых компьютеров ведущее место среди производителей процессоров занимают 2 фирмы: Intel и AMD. Им было присвоено основное имя, переходящее от модели к модели. У Intel - это Pentium и модель с урезанной кэш-памятью Pentium Celeron; у AMD - это Athlon и модель с урезанной кэш-памятью Duron [19].

Разрядность процессора - это максимальное количество битов информации, которое может быть обработано и передано процессором одновременно. Разрядность процессора определяется разрядностью регистров, в которые помещаются обрабатываемые данные. Например, если регистр имеет разрядность 2 байта, то разрядность процессора равна 16 (2x8); если 4 байта, то 32; Если 8 байт, то 64 [9].

Существует множество различных подходов к реализации структурной схемы (архитектуры) центрального процессора (ЦП). В нашей стране наибольшее распространение получила архитектура, предложенная американской фирмой Intel. Именно поэтому мы сосредоточимся на изучении процессоров, построенных на идеологии Intel, и компьютеров, реализованных на базе этих процессоров фирмой IBM.

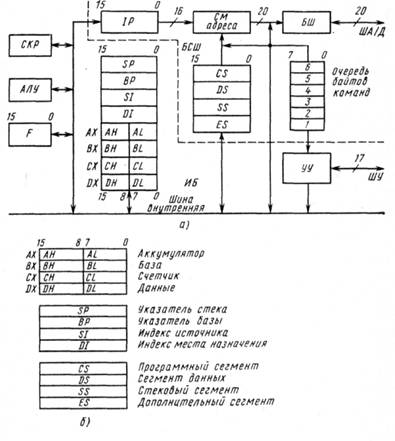

При разработке Intel8086 были применены интересные архитектурные решения, которые, в частности, включают разделение функций интерфейса шины и выполнение команд. Согласно этому, структура процессора (рисунок 1) можно разделить на две части: блок интерфейса шины (BSSH) и исполнительный блок (IB) [5].

Рассмотрим назначение и работу отдельных узлов микропроцессора Intel 8086. Он имеет четырнадцать 16-битных регистров, которые можно разделить на три группы в соответствии с их назначением. Регистры AH, BX, CX, DX образуют группу регистров общего назначения (POH) [9].

Эти регистры могут участвовать в арифметических и логических операциях без ограничений. Некоторые другие операции, такие как операции над цепочками байтов и слов, предписывают специальное использование регистрам этой группы: AH-накопитель, BX - база, CX - счетчик, DX - данные. В отличие от регистров других групп, РОН обладают свойством раздельной адресации высоких и низких байтов. Поэтому RON можно рассматривать как набор из двух наборов 8-битных регистров: набор H, содержащий АН, ВH, CH, DH, и набор L, содержащий AL, BL, CL, DL. Регистры всех остальных групп являются неделимыми и работают на 16-битных словах, даже если используется только самый высокий или самый низкий байт [11].

Рисунок 1. Архитектура центрального процессора Intel 8086 и его регистры [7]

Регистры SP, BP, SI и DI образуют группу индексных и индексных регистров, предназначенную для хранения значений смещения, используемых для адресации в текущем сегменте памяти. В этом случае указательные регистры SP и BP хранят смещения адресов в текущем сегменте памяти, выделенном для стека, а индексные регистры SI и DI содержат смещения адресов в текущем сегменте памяти, выделенном для данных. С этим связаны обозначения регистров: SP-указатель стека, BP-указатель основания, SI-индекс источника и DI-индекс назначения. Регистры этой группы также могут использоваться в качестве регистров общего назначения [7].

Регистры CS, DS, SS и ES, которые образуют группу сегментных регистров, играют важную роль во всех действиях по адресации памяти процессора. Обозначения регистров расшифровываются следующим образом: CS-кодовый или программный сегмент, DS-сегмент данных, SS-сегмент стека и ES-дополнительный сегмент [2]. Содержимое любого из этих регистров определяет текущий начальный адрес сегмента памяти, выделенного Пользователем для информации, соответствующей имени регистра.

Содержимое регистра CS определяет начальный адрес сегмента памяти, в котором находится объектный код программы. Следующая команда извлекается относительно содержимого CS с помощью значения указателя команды IP. Содержимое регистра DS определяет начальный адрес текущего сегмента данных, так что доступ к данным в памяти процессора осуществляется относительно содержимого DS. Для доступа к остальным трем сегментам-необязательному, стековому или программному-используется специальный указатель, который называется префиксом замены сегмента и находится в соответствующих командах [6].

Содержимое регистра SS определяет текущий сегмент, выделенный для организации стека. Все обращения к памяти, которые используют регистры BP или SP прямо или косвенно для вычисления адреса, выполняются относительно содержимого регистра SS. Такие вызовы включают, например, все операции стека, включая операции вызова подпрограмм, прерывания и операции возврата. Доступ к данным с использованием регистра BP (но не SP) также может быть осуществлен против одного из трех других сегментных регистров с помощью префикса замены сегмента [11].

Содержимое регистра ES определяет начальный адрес сегмента, рассматриваемого как дополнительный сегмент данных. В частности, доступ к данным в операциях с байтовыми или словесными цепочками осуществляется относительно ES, а содержимое DI берется в качестве смещения.

Помимо этих регистров, существуют два 16-разрядных регистра: IP-указатель команды и регистр F-флага. В IP регистре, формируется относительный (по отношению к CS) - адрес команды, которая должна быть выполнена. В регистре F используются следующие девять цифр: CF-перенос, PF-четность, AF-вспомогательный перенос, ZF-нулевой результат, SF-знак, TF-шаговый режим, IF-разрешение прерывания, DF-направление, OF-переполнение. Неиспользуемые биты на рисунке заштрихованы [9].

Флаги AF, CF, PF, SF и ZF характеризуют признаки результата последней арифметической, логической или иной операции, влияющей на эти флаги. Флаг устанавливается в следующих случаях:

AF - при выполнении операции «1» переносится из младшей байтовой тетрады в старшую или» 1 « заимствуется из старшей тетрады;

CF - при передаче «1» из старшего бита байта (слова) или при заимствовании одного из них в старший бит;

PF - если представление результата операции содержит четное число единиц измерения;

SF - при получении «1» в самом высоком бите результата;

ZF - если результат операции равен нулю [2].

В эту группу флагов также входит флаг OF, который устанавливается при переполнении в результате арифметических операций над знаковыми числами.

Флаги DF, IF и TF используются для управления работой процессора. Флаг DF управляет направлением обработки данных в операциях цепочки байтов или слов. При DF=1 цепочка обрабатывается снизу вверх, т. е. происходит автоматическое уменьшение (автоинкремент) адреса текущего элемента цепочки. При DF=0 цепочка обрабатывается сверху вниз, т. е. происходит автоматическое увеличение (автоинкремент) адреса [12].

Основные операции обработки данных выполняются в арифметико-логическом устройстве (АЛУ), которое связано со схемой коррекции результатов (СКР), используемой при работе с данными, представленными в двоично-десятичных кодах. Связь внутренних процессорных узлов с шиной SHA/D осуществляется через шинный буфер BS, состоящий из двунаправленных усилителей с тремя стабильными выходными состояниями.

Усовершенствование архитектуры Intel 8086 также связано с внедрением в структуру микропроцессора специального сумматора для вычисления адресов памяти [9].

Как отмечалось выше, разрядность адресов микропроцессора составляет 20. Однако для упрощения хранения и пересылки адресной информации процессор манипулирует 16-битными логическими адресами, которые включают начальные (базовые) адреса сегментов памяти и значения смещения в этих сегментах. Логические адреса используются для вычисления 20-битных физических (абсолютных) адресов с помощью следующей процедуры. Содержимое каждого сегментного регистра обрабатывается как 16 старших разрядов A19-A4 начального адреса соответствующего сегмента. Младшие биты A3-A0 этого адреса всегда считаются равными нулю и поэтому не хранятся в регистрах, а назначаются справа на старшие биты во время операции вычисления физического адреса [14]. Эта операция выполняется сумматором адресов, расположенным в блоке BSS, и состоит из сложения 20-битного начального адреса сегмента с 16-битным смещением, которое дополняется четырьмя старшими битами A19-A16, равными нулю, как показано на фиг. 1.3. Сумматор адресов выполняет, например, следующие вычисления: CS + IP - при выборе следующей команды, SS + SP - при обращении к стеку, DS + SI и ES + DI - при обработке строк, DS + EA-при обращении к оперативной памяти (EA-исполнительный адрес, формирование которого описано ниже) [9].

Поскольку наименьшие четыре цифры начального адреса любого сегмента должны быть равны нулю, значения начальных адресов сегментов выбираются как кратные 16. Максимальный объем памяти, выделенной для одного сегмента, определяется максимальным значением 16-битного смещения и составляет 64 КБ байт [22].

Таким образом, в простых системах с объемом памяти не более 64 КБ можно отказаться от сегментации памяти и установить все регистры сегментов в ноль. В этом случае 16-битный адрес смещения фактически будет абсолютным адресом. При использовании системы с большим объемом памяти (до 1м байт включительно) начальные адреса сегментов задаются исходя из особенностей структуры программного обеспечения и данных, хранящихся в памяти.

2 ФУНКЦИИ ЦЕНТРАЛЬНОГО ПРОЦЕССОРА

Процессор представляет собой кремниевую пластину с несколькими сотнями контактов, в которой размещается несколько миллионов транзисторов. Количество контактов определяется разъемом материнской платы. Транзисторы и контакты размещены в корпусе, на котором установлен радиатор с вентилятором (такая конструкция называется кулером, от англ. с Cooler-охладитель) [17].

Принцип работы процессора заключается в следующем. Данные, с которыми работает процессор, помещаются в его регистры (память процессора) или микрокоманды, в оперативную память ПК. Если информация хранится во внешних запоминающих устройствах, например на жестком диске, то она должна быть считана в оперативную память, с нее-в кэш процессора, и только потом в регистры процессора. Микрокоманды процессора вводят числа в свои регистры, обрабатывают их, а затем выводят результат, например, в оперативную память. Чтобы сложить целые числа 5 и 3, Процессор, помимо них, получает команду «сложить числа». На выходе получается результат-целое число 8 [12].

Архитектура современных ПК основана на магистрально-модульном принципе. Модульная архитектура предполагает магистральный (шинный) принцип обмена информацией между устройствами посредством следующих шин:

- данных;

- адреса;

- управления [11].

Физически шины представляют собой многопроволочные линии.

Шина данных. На этой шине данные, такие как блоки информации, считанные из ОЗУ, могут быть переданы процессору, а затем после обработки отправлены обратно в ОЗУ для временного хранения. Основной характеристикой шины данных является битовая скорость, которая определяется битовой скоростью процессора (количеством двоичных битов, обрабатываемых за такт). Чем выше битовая глубина, тем больше пропускная способность. Процессоры x486 имели 32-разрядные шины данных, Pentium 64 - разрядные и Pentium II dual 64 – разрядные [15].

Шина адреса. Известно, что каждое устройство ПК или ячейка ОЗУ имеет свой собственный адрес. Процессор выбирает устройства или ячейки памяти, в которые он записывает или считывает информацию по шине данных. Адрес передается по адресной шине только в одном направлении от процессора к оперативной памяти и устройствам.

Разрядность адресной шины определяет количество ячеек ОЗУ с уникальными адресами, которое может быть вычислено по формуле 2P, где p-разрядность адресной шины. Например, для 32-разрядной адресной шины число адресуемых ячеек памяти составляет 4 294 967 296 (232) [9].

Шина управления. Управляющая шина передает сигналы, определяющие характер обмена информацией. Управляющие сигналы определяют, какую операцию выполнять, синхронизируют обмен информацией между устройствами и т.д. [16].

Почти все время работы процессора связано с оперативной памятью, из которой извлекаются и вводятся данные (операнды), подлежащие обработке. Поэтому работа делится на несколько этапов, и их результаты сохраняются. Эти схемы используют собственную память процессора (регистры).

Все операции обработки данных в процессоре выполняются командами, представленными в определенном формате-комбинации размеров всех полей и их расположения в команде. Команда разделена на два направления:

- область кода операции (указывает, что нужно сделать вообще);

- адрес области (операнд, с помощью которого это должно быть сделано).

Адресная область состоит из трех полей: в первых двух хранятся адреса операндов, а в третьем-адрес результата действия над операндами [4].

В двухадресных командах область адреса состоит из двух полей: поля адреса первого и второго операндов, а адрес результата записывается в поле адреса первого операнда. В одноадресных командах адресная область состоит из одного поля, содержащего адрес операнда, и адрес второго операнда и результат такой же, как сумматор. Есть также безадресные команды.

Существует несколько типов адресации одного операнда:

- прямая адресация (вместо адреса операнда команда задает сам операнд (целое число));

- полный или абсолютный тип адресации (команда задает полный адрес ячейки, в которой находятся данные);

- косвенная адресация (в поле адреса операнда можно указать адрес регистра или ячейки памяти, где хранится тот же адрес, по которому можно найти ячейку с нужным операндом). Количество ссылок (или переходных шагов) называется глубиной косвенной адресации [3].

Для нескольких операндов или массивов обычно указываются адрес массива и номер (индекс) элемента. Начальный адрес указывается в команде, где также имеется поле с номером регистра, содержащее значение индекса или номер ячейки в массиве относительно начального адреса-модификация адреса. Существует также относительная адресация, когда регистр задает начальный адрес, в команде-адрес этого регистра и смещение относительно начального адреса. Все остальные адреса операндов будут получены суммированием адреса и смещения.

Первые регистры процессора могли хранить только 4-разрядные числа. Затем появились 8-и 16-битные процессоры, с появлением процессора X386 был реализован 32-битный режим, который позволял работать с числами размерности свыше двух миллиардов [8].

Это статическая память (Stati-RAM-SRAM), которая, в отличие от динамической памяти, не требует периодической регенерации (обновления). Время доступа к этой памяти составляет не более 2 НС., т. е. он может работать синхронно с процессором на частоте 500 МГц и более. Контроллер кэша находится в чипе Северного моста чипсета материнской платы [15].

В процессорах x386 кэш-память объемом 128 КБ располагалась на материнской плате. Начиная с процессоров x486, в процессоре появился дополнительный кэш, работающий на его частоте,-кэш первого уровня (LevelI-LI). На материнской плате установлен кэш второго уровня (L2). В большинстве современных процессоров кэш Li и L2 встроен в ядро процессора. И если в PentiumII и PentiumIII кэш второго уровня работает на половине частоты процессора, то у Celeron, AMDK6 - III, Athlon и PentiumIV-на частоте процессора, что положительно сказывается на производительности.

Первой такой выделенной технологией можно считать MultiMediaeXtension (MMX) - расширение базового набора команд процессора (57 команд для обработки графики и звука). Одна команда может обрабатывать много данных, что значительно повышает производительность (SIMD-SingleInstruction, ManyData-одна команда, много данных) [11].

При работе с командами MMX данные хранятся в регистрах сопроцессора, что означает невозможность выполнения операции с плавающей запятой при выполнении программы MMX. Кроме того, команды MMX предназначены только для работы с целыми числами.

От технологии SIMD пришли две конкурирующие системы для потоковой обработки данных.

Так, в процессорах AMDK6-2, помимо блока MMX-commands, был добавлен блок 3DNow!, отвечающий за обработку трехмерных изображений. Он включает в себя 27 новых команд для обработки чисел с плавающей запятой, и в отличие от MMX, 3DNow! Не поддерживает работу процессора [1].

Процессоры Pentium II представили универсальный мультимедийный ускоритель, работающий по принципу SIMD, но не зависящий от ядра. Это стало возможным благодаря новому блоку SSE (Streaming SIMD Extensions - stream SIMD extension). Он состоит из 70 команд, управляющих 8 специальными 128-битными регистрами. SSE позволяет выполнять одновременные операции с содержимым двух регистров [9].

До недавнего времени увеличение быстродействия процессоров было связано исключительно с увеличением их тактовой частоты и размера кэша. Но одновременное выполнение нескольких потоков также приводит к увеличению быстродействия процессора, причем более значительному. Именно в обработке нескольких потоков и заключается суть новой технологии Hyper - Threading.

Как известно, процессор оперирует набором из нескольких команд, которые необходимо выполнить. Для этого используется счетчик команд, который указывает места в памяти, где хранится следующая команда, подлежащая выполнению. После каждой команды значение этого регистра увеличивается, пока поток не завершится [9]. В конце выполнения потока в счетчик команд вводится адрес следующей выполняемой инструкции. Потоки могут прерывать друг друга, но процессор запоминает значение счетчика команд в стеке и загружает новое значение в счетчик. Хорошо известный способ решения этой проблемы заключается в использовании двух процессоров-если один процессор может выполнять один поток одновременно, то два процессора могут выполнять два потока одновременно. Возможность распределять выполнение нескольких потоков по ресурсам компьютера называется многопоточностью.

Нечто похожее на многопоточность предлагает новая технология от Intel под названием Hyper-Threading. Он появился в ответ на проблему неполного использования исполнительных блоков процессора. Hyper-Threading-это название технологии одновременной многопоточности (SimultaneousMulti-Threading-SMT). Один физический процессор по существу эмулирует ОС как два логических. В Гиперпоточном процессоре каждый логический процессор имеет свой собственный набор регистров (включая отдельный счетчик команд), и чтобы не усложнять технологию, он не реализует одновременное выполнение некоторых команд в двух потоках [6].

Когда команды извлекаются из кэша (или ОЗУ), они должны быть декодированы и отправлены на выполнение. Эти операции (получение команд, декодирование и отправка на выполнение) выполняются на препроцессоре. Из препроцессора они направляются в постпроцессор, где и выполняются. После этого результат возвращается в кэш (ОЗУ) [14].

Как вы можете видеть, весь процесс обработки команд состоит из четырех шагов, которые определяют так называемый 4-ступенчатый процесс (конвейер).

1. Извлечение из кэша (ОЗУ).

2. Декодирование (разборка команды).

3. Выполнение команд (применение действий).

4. Запись в кэше (ОЗУ).

Каждый из этих шагов команда должна пройти ровно один такт. Поэтому, чем быстрее каждый из этапов выполняет свои функции, тем быстрее работает весь процессор и тем выше его тактовая частота. Выполнение всех этих четырех команд определяет цикл. Большинство процессоров выполняют команды в одном цикле, но есть сложные команды, которые требуют нескольких циклов. При выполнении сложных команд различные устройства используют свои собственные конвейеры выполнения, тем самым добавляя еще несколько шагов к основному конвейеру процессора. Количество ступеней определяет глубину конвейера [3].

В отличие от классического варианта, когда весь конвейер состоит из четырех ступеней, в большинстве современных процессоров конвейер разделен на семь и более ступеней (гиперконвейерная обработка), что требует более высокой тактовой частоты.

Технология обработки гипертония предполагает удвоение длины конвейера по сравнению с предыдущей микроархитектурой P6. например, один из основных элементов трубопровода-блок прогнозирования и восстановления ветвей-разделен на 20 циклов [9].

В Pentium на этапе исполнения используется меньше функциональных блоков процессора. Но каждый из них имеет более длинный и более короткий трубопровод. Процессор Pentium может одновременно выполнять 126 команд на разных этапах. Кроме того, в Pentium IV кэш первого уровня секционирован, и его кэш команд фактически находится на препроцессоре. Он называется tracecache и влияет как на конвейер, так и на основной поток команд. Этот кэш содержит декодированные команды x86 (микрокоманды), что исключает задержку в расшифровке кодов команд. Процессорные исполнительные устройства получают непрерывный поток команд, и общее время восстановления значительно сокращается в случае неправильного предсказания ветвления [2].

В процессорах с микроархитектурой x86, таких как Pentium II или Athlon, команды поступают в декодер из кэша команд, где они разбиваются на более мелкие части (микрокоманды). Эти микрокоманды используются при внеочередном выполнении команд, исполнительное устройство выполняет их планирование,выполнение и сброс. Это разделение происходит, когда процессор выполняет инструкцию.

Кэш команд pentiumi v получает переведенные и декодированные микрокоманды, готовые к передаче для экстраординарного выполнения, и формирует из них мини - программы («следы») [6].

По завершении работы препроцессор накопленных дорожек кэш-трека отправляет до трех микроопераций в сутки на экстраординарную производительность устройства. В этом случае команды не нужно переводить или декодировать. И только в случае пропуска кэша первого уровня (L1) препроцессор начнет отбирать и декодировать инструкции из кэша второго уровня (L2) - к основному конвейеру добавляются дополнительные 8 шагов.

Кэш отслеживания работает в двух режимах [3]:

- Исполнительный (executemode);

- построение сегментов трекинга (tracesegmentbuildmode).

В режиме выполнения кэш L1 отправляет команды исполнительным устройствам. Когда этот кэш промахивается, он переходит в режим отслеживания сегмента. В этом режиме препроцессор выбирает команды из кэша L2, преобразует их в микрокоманды, создает сегмент отслеживания, который затем перемещается в кэш с отслеживанием и затем выполняется. Кэш L2 объемом 256 кб с улучшенной передачей данных ускоряет обмен информацией между кэшем уровня 2 и ядром процессора [5].

Улучшенная система динамического выполнения-это сложное устройство для хранения команд для исполняемых файлов. Эта система позволяет исполнителям выбирать команды из большого набора предстоящих операций.

Таким образом, как отмечалось выше, процессор начинает декодирование только в случае пропуска кэша L1. Поэтому он предназначен для декодирования только одной команды x86 за такт. Поскольку все команды x86 декодируются в 2 или 3 микрокоманды, чтобы не засорять кэш отслеживанием, действуйте следующим образом. Как только кэш отслеживания встречает длинную инструкцию x86 при создании сегмента отслеживания, он вставляет метку в сегмент отслеживания, которая указывает места памяти с последовательностью микроинструкций инструкции. В режиме выполнения, когда кэш с отслеживанием передаст поток команд на стадию выполнения, если он попадет в такую метку, он приостановит работу и временно передаст управление потоком команд на микрокод ОЗУ.

3 КЛАССИФИКАЦИЯ ПРОЦЕССОРОВ

Семейство Pentium

Р5. Первый процессор с двухконвейерной структурой, выпускался под Socket 4; кэш - память - 16 Кб; 3,1 млн. транзисторов; технология производства - 0,8 мкм; тактовая частота - 60 - 66 МГц; L1 - 16 Кб; L2 на матричной плате - до 1 Мб; процессор 64 - разрядный; шина данных 64 - разрядная (60 - 66 МГц); адресная шина 32 - разрядная; общая разрядность – 32 [7].

Р54. 3,3 млн. транзисторов; технология производства - 0,5 - 0,35 мкм; тактовая частота - 75 - 200 МГц; L1 - 16 Кб; L2 на матричной плате - до 1 Мб; процессор 64 - разрядный; шина данных 64 - разрядная (50 - 66 МГц); адресная шина 32 - разрядная; разъем Socket 5, позднее Socket 7.

Р55С. Расширение MMX (Multi-Media eXtention), содержащее 57 команд для вычислений с плавающей точкой, увеличивающее производительность компьютера в мультимедиа приложениях; 4,5 млн. транзисторов; технология производства - 0,28 мкм; тактовая частота - 166 - 233 МГц; L1 - 32 Кб; L2 на матричной плате - до 1 Мб; процессор 64 - разрядный; шина данных 64 - разрядная (60 - 66МГц); адресная шина 32 - разрядная; общая разрядность - 32; разъем Socket 7 [9].

Семейство Pentium Pro

Pentium P6. Создавался как процессор для серверов и рабочих станций, имеет объединенный в одном корпусе L2 объемом 256Кб; 5,5 млн. транзисторов; технология производства - 0,35 мкм; тактовая частота - 150 - 200 МГц.

Klamath. Первый процессор линейки Pentium II и первая модель с разъемом Slot 1; технология - 0,35 мкм; тактовые частоты ядра - 233 - 300 МГц; частота шины - 66 МГц; L1 - 32 Кб; L2 - 512 Кб; конструктивное исполнение - картридж SECC [3].

Deschutes. Ядро процессор линейки Pentium II, сменившего Klamath; технология - 0,25 мкм; тактовые частоты ядра - 233 - 300 МГц; частота шины - 66 МГц; L1 - 32 Кб; L2 - 512 Кб; тактовая частота - 266 - 450 МГц; частота шины - 66 - 100 МГц; L2 на процессоре - 521 Кб. Разъем Slot 1; конструктивное исполнение - картридж SECC, который в старших моделях был сменен на SECC2.

Katmai. Ядро процессора Pentium III, пришедшего на смену Deschutes. Добавлен блок SSE (Streaming SIMD Extensions), расширен набор команд MMX, усовершенствован механизм потокового доступа к памяти. Технология - 0,25 мкм; тактовая частота - 450 - 600 МГц; L2 на процессоре - 512 Кб; частота шины - 100 МГц; разъем - Slot 1 [7].

Coppermine. Ядро процессоров Pentium III и Celeron; технология - 0,18 мкм; 256 Кб L2 для PentiumIII и 128 Кб - для Celeron. Частота - от533 МГц и выше. Наряду с FSB100 МГц версиями Pentium III выпущены и варианты FSB133 МГц. Последние процессоры, рассчитанные на Slot 1, постепенно были вытеснены изделиями в конструктивном исполнении FC - PGA 370, рассчитанными на разъем Socket 370. частота шины для процессоров Celeron - 66 МГц, а начиная с модели Celeron 800 - 100 МГц.

Tualatin - 256K. Кодовое наименование ядра и процессоров Socket 370 PentiumIII, сделанных по технологии 0,13 мкм. Рабочая частота моделей для Desktop с частотой системной шины 100 МГц - 1,1 ГГц [9].

Семейство Celeron

Covington. Первый процессор линейки Celeron. Построен на ядре Deschutes и выпускался по 0,25 - микронной технологии. Тактовая частота - 266 - 300 МГц; частота системной шины 66 МГц; L1 - 32 Кб; Slot 1.

Mendocino. L2 - 128 Кб, интегрированная на одном кристалле с ядром. Тактовая частота - 300 - 533 МГц; частота системной шины - 66 МГц; технология 0,25 мкм для Slot 1, 0,22 мкм - для Socket – 370 [3].

Coppermine 128K. Начиная с частоты 533 МГц, у Celeron появилось ядро - Coppermine с урезанным до 128 Кб кэшем L2. по своим характеристикам этот процессор максимально близок к PentiumIII, построенному на базе Coppermine, в том числе впервые для Celeron включает поддержку SSE. Частота процессора - 900 МГц и выше; технология 0,13 мкм; частота системной шины - 100 МГц.

Willamette - 128. Технология 0,18 мкм; тактовая частота - 1,6 - 2 ГГц; L1 - 8 Кб; L2 - 128 Кб; процессор 64 - разрядный; шина данных 64 - разрядная (400 МГц); разъем Socket 478 [7].

Семейство Pentium IV

Willamette 423. Процессор с гиперконвейеризацией (hyperpipelining) - с конвейером, состоящим из 20 ступеней. Технология 0,18 мкм; тактовая частота процессора - 1,3 - 2 ГГц; L1 - 8 Кб; L2 - 256 Кб; процессор 64 - разрядный; шина данных 64 - разрядная (400 МГц); разъем Socket 423.

Willamette 478. Технология 0,18 мкм; тактовая частота - 1,3 - 2 ГГц; L1 - 8 Кб; L2 - 256 Кб (полноскоростной); процессор 64 - разрядный; шина данных 64 - разрядная (400 МГц); разъем Socket 478.

Northwood. Производится с соблюдением технологических норм 0,13 мкм в 478 - контактном корпусе форм - фактора mPGA478 (FC - PGA2). Особенностью процессора является специальная алюминиевая пластина над кристаллом, которая одновременно выполняет функции теплоотвода и экранирующего элемента.

Prescott. Наследник ядра Northwood, будет изготавливаться по технологии 90 нм, частота системной шины 667 МГц, поддержка Hyper - Threading, Socket 478. Наследник ядра Prescott – Tejas [9].

Процессоры Intel для серверов

Xeon. Официальное наименование линейки процессоров для мощных серверов и рабочих станций. Первые варианты были построены на ядре Deschutes. Технология - 0,25 мкм; Slot 2; L2 имеет объем 512, 1024, 2048 Кб.

Tanner. Pentium III Xeon. Тактовая частота от 500 МГц; частота системной шины 100 МГц; CSRAM - кэш второго уровня объемом 512, 1024, 2048 Кб. Поддерживается MMX и SSE; L1 - 32 Кб [3].

Cascades. Pentium III Xeon, созданный по технологии 0,18 мкм. Это серверный вариант Coppermine. На чипе содержится L2 - 256 Кб; тактовая частота от 600 МГц; частота шины процессора - 133 МГц.

Pentium III - S. Процессоры с ядром Tualatin; технология - 0,13 мкм; кэш L2 - 512 Кб; рабочие частоты - с 1,13 ГГц. Предназначены для двухпроцессорных конфигураций.

Foster. Pentium IV в серверном варианте. Тактовая частота - 100 МГц при передаче данных с частотой 400 МГц; Socket 603 [7].

Prestonia. Pentium IV в серверном варианте, созданный по технологии 0,13 мкм. Основную систему составляет специальный чипсет Plumas. Частота первых моделей процессора - 2,20 ГГц.

Nocona. Xeon с новым ядром, изготовленным по технологии 90 нм. Ядро PentiumIV, Prescott; L2 - 1 Мб; тактовая частота системной шины 533 - 667 МГц [9].

Семейство Pentium V

Nehalem. Производится по технологии 90 нм, а в конце 2015 г. - планировалось и по технологии 65 нм.

Новые процессоры, называемые Core i, изготавливаются по 45-нм технологическим стандартам с использованием высокочастотных диэлектрических и металлических вентильных транзисторов, но в отличие от своих предшественников все четыре ядра расположены на одном кристалле. Core 2 Quad состоит из двух ядер Core 2 Duo, объединенных в одном корпусе. Кроме того, процессоры Nehalem содержат кэш-память третьего уровня объемом 8 Мбайт, встроенный трехканальный контроллер памяти DDR3 и шинный контроллер Quick Path Interconnect (QPI), что потребовало значительного увеличения контактов – до 1366, именно поэтому размер процессора нового поколения стал больше и по форме он уже напоминает прямоугольник, а не квадрат, как у Core 2. Естественно, ни о какой совместимости разъемов речи не идет [22].

Кстати, название Core i7 отражает поколение процессоров, использующих архитектуру P6. В настоящее время доступны три новые модели процессоров: Core i7-965 Extreme Edition, Core i7-940 и Core i7-920. Главным отличием между ними является рабочая частота ядер и шины QPI, которая заменила старую FSB, аналогичную технологии AMD. Естественно, экстремальная версия ориентирована на энтузиастов и оверклокеров, имеет более высокую частоту и разблокирована для увеличения множителя. Также для Core i7-965 Extreme Edition характерно большее количество умножителей для памяти, частота которых формируется путем умножения их на тактовую частоту (опорную частоту шины QPI или QPI bclk), равную 133 МГц. Частоты ядра, шины QPI и кэша L3 также формируются путем умножения определенных коэффициентов на опорную частоту. Если вы разгоняете процессор, повышая QPI bclk, частота всех блоков и памяти будет расти в зависимости от их множителей. Обычный Intel Core i7 не будет столь дружелюбен к оверклокерам, но, возможно, со временем эта проблема все же будет решена [22].

Еще одним нововведением семейства Nehalem стало использование технологии Hyper-Threading (или одновременной многопоточности-SMT, одновременная многопоточность), от которой отказались при переходе на базовую архитектуру. Теперь каждый процессор Core i7 определяется как восемь логических ядер, что позволяет значительно повысить производительность приложений, оптимизированных для многопоточности [14].

Несмотря на перенос части северного моста на процессор, уровень TDP не превышает 130 Вт, что даже ниже, чем у 45-нм Intel Core 2 Extreme QX9770 на недавно выпущенном stepping C0. Это связано с солидностью кристалла, а с меньшим кэшем-у QX9770 он составляет 12 МБ, в то время как Core i7 удовлетворяет кэш-память с общим объемом 9 МБ. Но даже при таком уровне TDP системы охлаждения для новых процессоров немного выросли в размерах, а монтажные отверстия в материнских платах не соответствуют креплениям от кулеров под сокетом LGA775. Учитывая, что сейчас процессоры в большинстве случаев поставляются в коробочном исполнении, вряд ли стоит об этом беспокоиться. Для разгона, конечно, придется найти кулер поэффективнее или крепление для старой, но мощной системы охлаждения [8].

Таким образом, даны определения микропроцессора и микропроцессорной системы, принципы и устройства микропроцессора. Дана классификация микропроцессоров по их архитектуре, представлены параметры, характеризующие микропроцессоры каждого класса как вычислительное устройство и как электронный продукт. Описаны структура и основные блоки микропроцессора i486, который является базовым микропроцессором для данной архитектуры. В статье также рассмотрены классические направления повышения производительности микропроцессоров, показаны их ограничения. Представлены современные пути развития универсальных микропроцессоров.

ЗАКЛЮЧЕНИЕ

Данная курсовая работа посвящена изучению архитектуры, функционирования центрального процессора персонального компьютера.

В первом разделе работы дано определение центрального процессора, даны Основные характеристики. В работе представлена схема структуры процессора, описана работа основных регистров.

Второй раздел посвящен принципам работы центрального процессора персонального компьютера. В разделе показан общий рабочий цикл процессора, который состоит из 23 шагов. Описаны форматы команд, которые могут быть: однобайтовая одноадресная команда, двухадресная команда с постбайтовой адресацией и одноадресная команда с постбайтовой адресацией. Приведена также схема центрального процессора и алгоритм функционирования.

В третьем разделе представлены основные характеристики процессоров семейства AMD и Intel. Проведен сравнительный анализ основных характеристик процессоров.

Таким образом, задачи решены, цель достигнута

СПИСОК ИСПОЛЬЗОВАННЫХ ИСТОЧНИКОВ

1. Данилин, Александр Архитектура и стратегия. «Инь» и «янь» информационных технологий / Александр Данилин , Андрей Слюсаренко. - М.: Интернет-университет информационных технологий, 2019. - 506 c.

2. Задков, В. Н. Компьютер в эксперименте: архитектура и программные средства систем автоматизации / В.Н. Задков, Ю.В. Пономарев. - М.: Главная редакция физико-математической литературы издательства «Наука», 2017. - 376 c.

3. Заика, Александр BIOS. Разгон и оптимизация компьютера / Александр Заика. - М.: Питер, 2017. - 666 c.

4. Зозуля, Юрий Настройка компьютера с помощью BIOS на 100% / Юрий Зозуля. - М.: Питер, 2019. - 368 c.

5. Кирсанов, Э. Ю. Нейрокомпьютеры с параллельной архитектурой. Книга 16 / Э.Ю. Кирсанов. - М.: Радиотехника, 2018. - 221 c.

6. Комиссарова, Валерия Программирование драйверов для Windows / Валерия Комиссарова. - М.: БХВ-Петербург, 2018. - 834 c.

7. Крейгон, Х. Архитектура компьютеров и ее реализация / Х. Крейгон. - М.: Мир, 2016. - 416 c.

8. Куличков, А.В. Импульсные блоки питания для IBM PC. Выпуск 22 / А.В. Куличков. - М.: Книга по Требованию, 2016. - 120 c.

9. Мэтт, Ричардсон Заводим BeagleBone / Ричардсон Мэтт. - М.: Амперка, 2015. - 669 c.

10. Олег, Вальпа Полезные схемы с применением микроконтроллеров и ПЛИС (+ CD-ROM) / Вальпа Олег. - М.: Додэка-XXI, 2018. - 399 c.

11. Открытые системы. СУБД 3/2013. - М.: Открытые Системы, 2017. - 771 c.

12. Паттерсон, Д. Архитектура компьютера и проектирование компьютерных систем / Д. Паттерсон, Дж. Хеннесси. - М.: Питер, 2019. - 784 c.

13. Попов, С. Н. Аппаратные средства мультимедиа. Видеосистема PC / С.Н. Попов. - М.: БХВ-Петербург, 2019. - 400 c.

14. Предко, Майкл PIC-микроконтроллеры. Архитектура и программирование / Майкл Предко. - М.: ДМК Пресс, 2016. - 506 c.

15. Рец, К. П. Как восстановить файлы и данные с жесткого диска, флешки, «плохих»/поврежденных CD/DVD, восстановить фотографии, удаленные из цифрового фотоаппарата, восстановить данные с мобильного телефона, пароли к ICQ, пароли к архивам, документам и т.д. (+ DVD-ROM) / К.П. Рец, Р.Г. Прокди, М.И. Рыжкова. - М.: Наука и техника, 2019. - 256 c.

16. Смирнов, Юрий Секреты восстановления жестких дисков ПК / Юрий Смирнов. - М.: БХВ-Петербург, 2015. - 879 c.

17. Смирнов, Юрий Секреты эксплуатации жестких дисков ПК (+ CD-ROM) / Юрий Смирнов. - М.: БХВ-Петербург, 2016. - 416 c.

18. Соломенчук, В.Г. Аппаратные средства PC / В.Г. Соломенчук. - М.: БХВ-Петербург, 2016. - 935 c.

19. Таненбаум, Э. Архитектура компьютера (+ CD-ROM) / Э. Таненбаум. - М.: Питер, 2015. - 848 c.

20. Ташков, Петр Сбои и ошибки ПК. Лечим компьютер сами / Петр Ташков. - М.: Питер, 2019. - 176 c.

21. Трасковский, А. Сбои и неполадки домашнего ПК / А. Трасковский. - М.: БХВ-Петербург, 2015. - 712 c.

22. Трасковский, Антон BIOS. Наиболее полное руководство / Антон Трасковский. - М.: БХВ-Петербург, 2016. - 544 c.

23. Трасковский, Антон BIOS. Экспресс-курс / Антон Трасковский. - М.: БХВ-Петербург, 2016. - 288 c.

24. Фленов, Михаил Компьютер глазами хакера / Михаил Фленов. - М.: БХВ-Петербург, 2017. - 358 c.

25. Шафрин, Ю. IBM PC. Учебник / Ю. Шафрин. - М.: Бином. Лаборатория знаний, 2018. - 536 c.

- Анализ конкурентов на рынке и определение собственной конкурентоспособности ( на примере ЗАО “Тандер”)

- Формы и системы оплаты труда на предприятии (Анализ формы и организации системы оплаты труда на предприятии)

- Современный банковский маркетинг: методы и тенденции развития (Теоретические основы современного банковского маркетинга)

- Управленческие решения, их классификация

- Учет труда и заработной платы (Характеристика предприятия ООО "Нефтехимзаводмонтаж" и организация бухгалтерского учета)

- Маркетинговые структуры предприятия (теоретические аспекты) (Маркетинговые структуры предприятия)

- Оценка готовности детей к школе (Проблема психологической готовности ребенка к обучению в школе)

- Развитие творческих способностей дошкольников в условиях театрализованной деятельности (Понятие и сущность творчества, творческих способностей)

- Международный рынок минеральных ресурсов (Минеральные ресурсы: понятие и классификация)

- Управление финансами и пути его совершенствования в РФ (Объекты управления)

- Состав правонарушения (Соотношение правонарушения и состава правонарушения)

- Понятие и виды государственных пенсий(Понятие государственного пенсионного обеспечения)